pcb layout 基本规则

——

基本走线要求:

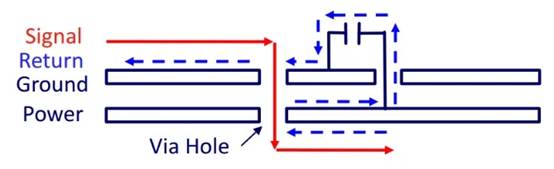

1. clk 部分不可过其它线, Via 不超过两个.

2. 不可跨切割,零件两Pad 间不能穿线.

3. Crystal 正面不可过线,反面尽量不过线..

4. Differential Pair 用最小间距平行走线.且同层

5 clk 与高速信号线(1394,usb 等)间距要大于50mil.

2. VGA:

基本走线要求:

1. RED、GREEN、BLUE 必须绕在一起,视情况包GND. R.G.B 不要跨切割。

2 HSYNC、VSYNC 必须绕在一起, 视情况包GND.

3. LAN:

基本走线要求

1. 同一组线,必须绕在一起。

2 Net: RX,TX:必须differential pair 绕线

4.1394:

基本走线要求:

1. Differential pair 绕线,同层,平行,不要跨切割.

2. 同一组线,必须绕在一起。

3 与高速信号线间距不小于50mil

5. USB:

基本走线要求:

1 Differential pair 绕线,同层,平行,不要跨切割.

2 同一组线,必须绕在一起

6. CPU-NB (AGTL):

基本走线要求:

1. 同组同层或同组不同层走线,绕线须同组绕在一起

2. 绕线时,同一NET 间距不小于四倍线寛

3. NET 长度要加入CPU & NB 的包装长度.

4. STB N/P(+/-) Differential Pair 绕线

5 VIA 类型为VIA26

7. CPU-SB:

基本走线要求:

1. 同一组线,必须绕在一起.

2 pull up 电阻,必须靠近 CPU

8. NB-DDR:

基本走线要求:

1.阻尼电阻和终端电阻(排阻)NET: MD & MA & DQS & DQM 不能共享.

2.同组同层走线,采用四倍间距绕线.

9. NB-AGP:

基本走线要求:

1.同组同层或同组不同层走线,绕线须同组绕在一起

2.绕线时,同一NET 间距不小于四倍线寛

3.STB +/- Differential Pair 绕线.

4 在constraint area 尽量按guide lauout .

10. NB-SB:

基本走线要求:

1 走在一起,不要跨切割线.

2.绕线时,同一NET 间距不小于四倍线寛

11. IDE:

基本走线要求:

1.同组同层,绕线须同组绕在一起.

2.绕线时,同一NET 间距不小于四倍线寛

12. PCI:

基本走线要求:

1PAD 与PAD 之间最多过三根线

2 电阻,电容尽量摆放整齐.

13. CNR:

基本走线要求:

1.走在一起.

14. POWER:

基本走线要求:

1 一般用30 : 5 走线,线宽40MIL 以上时间距不小于10MIL,VIA 为VIA40, (或打2个VIA24)

15. OTHER:

基本走线要求:

1. 所有IO 线不可跨层。

2. COM1,COM2,PRINT(LPT),GAME 同组走在一起。

3 COM1、COM2 先经过电容、再拉线出去。

16.加测试点:

1. 测试以100%为目标至少要加到98%以上.

2. pin to pin 间距最好为75mil 最低不小于50mil.

3. 测试点pad 最小为27mil,尽量使用35mil.

4. 单面测试点距同层零件外框的间距大于50MIL.

5. CPU 插座包括ZERO 拉杆,内部不可以放置Top Side Test Point

6. clk 前端不用加测试点.后端可将via 换成test_via.(须客户认同)

7. 不可影响Differential Pairs 绕线。

17. 修改DRC:

1. 完成DRC 检查,内层检查,未连接PIN 的检查.

2 所有net,不可短路.不可有多余的线段.

18. 敷铜箔.:

需要敷铜箔的零件,net 应正确敷铜箔.

19. 摆放文字面:

1. 文字面由左而右、由上而下标示, 方向一致.

2. 零件标示,距离零件越近越好

3. 正确摆放零件脚位,极性标示.

4. 零件符号是否标示。

CN、JP:脚位标示(注意方向) 。

零件极性:※电容:+ ※晶体:G、D、S ※二极管:A、K5 删除多余线段、标示

评论