下一代FPGA有望实现突破性优势

本白皮书介绍为什么电信带宽和基础设施促进了FPGA功能的增强,以及ASIC和ASSP面临的商业挑战,可编程逻辑器件(PLD)定制方法是怎样支持FPGA功能的跨越式发展。本文还简要介绍了下一代FPGA和SoC系列品。

本文引用地址:http://www.amcfsurvey.com/article/283452.htm引言

最新发布的FPGA是硬件规划人员、软件开发人员和系统设计人员实现其下一代产品目标的关键支撑因素。大量的电信基础设施成指数增长的带宽需求以及各行业使用这些带宽的需求使得现有硬件和软件解决方案很难满足性能要求,也难以达到成本和功耗目标。ASIC、ASSP和独立处理器遇到了发展瓶颈,PLD公司很难解决固有的成本问题。而同时,大量最终应用对带宽的要求越来越高,要求PLD公司通过不同的工具和选择来满足各种需求。通过这些选择并且能够高效应用它们的PLD公司将为硬件和软件开发人员带来突破性优势,帮助他们开发下一代产品。

日益增长的带宽和灵活性需求促使功能实现突破

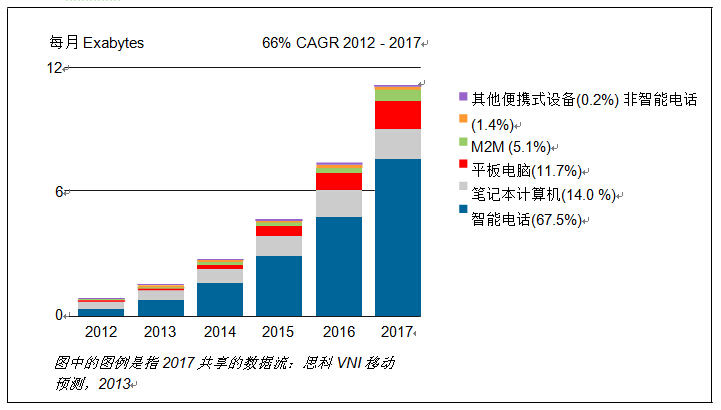

智能电话和其他便携式设备越来越多的功能是促使系统性能大幅度提高的原因所在,下一代FPGA将体现这些系统性能。移动带宽的爆炸式增长对无线、固网和数据中心体系结构功能产生了巨大的需求。智能电话数量增长速率呈个位百分比,而智能电话的功能越来越多,这些设备的用户不断要求提高带宽。这主要是高质量视频带宽需求造成的。2012年,智能电话数据平均使用量增长了81%。思科预计到2017年,移动流量每年会增长66%,三分之二的移动流量是视频内容。此时,移动网络速度将会提高七倍,4G网络承载了45%的流量(1) (参见图1)。

图1.思科预测到2017年,移动流量达到每月11.2 Exabytes

下面简要介绍了三种基础设施应用,在这些例子中,解释了为什么硬件和软件开发人员通过FPGA来实现其下一代产品带宽、性能、功耗和成本目标。

■ 无线远程射频单元

■ 400G固网通道卡

■ 数据中心

无线远程射频单元

在大投入的无线基础设施市场上,电信运营商要求带宽更高更快,而成本更低。速度越快,运营商的成本就越低,就可以部署更多的系统,覆盖更多的区域,为用户提供更快的服务——这是很大的优势。这些公司的产品策略是尽可能一直保持数据通路宽度不变,提高时钟频率。即将出现的远程射频单元将采用FPGA为复杂功能提供500 MHz内核性能,例如,实现数字预失真算法等。这保护了他们在射频体系结构上的投入,支持他们覆盖更宽的射频(RF)带宽。对此,他们寻求更好的投资回报,只需要很少的工作就能够完成重新规划解决方案。

而且,他们能够很快获得这些新产品,从而增强了产品及时面市优势。他们还需要降低运营成本,降低每比特的成本,这是因为每一移动用户的收入增长率要远远低于每一用户的数据流量增长率。这样,通过加宽数据通路,在更小而功效很高的FPGA上开发高功效设计,他们可以实现这一目标。

400G通道卡

提高FPGA性能的另一推动因素是更新网络通信基础设施的需求。下一代400G和现在的100G通道卡将极大的增强系统功能。下一代系统带宽增长四倍,远远大于以前的系统。

这类市场处于起步阶段,因此,公司不会冒险开发ASIC或者ASSP来实现这一目标。集成多个每秒56 gigabits (Gbps)和28 Gbps收发器解决方案可以满足这一带宽需求,但这只是解决方案的一部分。还需要更多、更快的逻辑来满足更高的带宽需求。但是,由于设备使用空间并没有改变,因此,功耗指标受限。网络基础设施不会接受功耗随带宽线性增长的解决方案。对于400G带宽每秒6亿数据包的包处理和流量管理应用,调整数据通路宽度和频率能够缓解数据通路处理功能,但是无法调整调度等控制通路处理功能。因此,在各方面都需要提高器件性能,包括:处理、存储器接口、IO接口,等等。FPGA一直是最吸引人的解决方案,但是公司要加大在每瓦高性能体系结构、收发器和工艺技术上的投入,大幅度增强功能,解决这一难题。

数据中心

通过这些新的无线设施上传或者下载的所有数据和视频会通过新的400G数据包处理基础设施,也需要进行存储和处理。计算功耗和计算成本是数据中心的关键指标。数据中心越来越多的使用了FPGA进行数据访问、计算和网络加速。数据中心服务器的瓶颈在于对数据的访问。最新的处理器内核越来越多,但是,外部存储器和数据带宽却跟不上计算能力的增长。很多服务器只达到平均利用率,距离峰值处理能力还很远。这些服务器非常适合采用FPGA进行加速。通过FPGA实现硬件加速是替代这些处理器的好方法,它解决了处理器软件无法克服的性能瓶颈。

其他应用也通过FPGA来满足其越来越高的带宽需求,例如,视频内容提供商转向4K视频,还有云计算和国防情报应用等。这些应用面临同样的问题。如果需要了解详细信息,请参考微软研究:加速大规模数据中心服务的可配置架构。

ASIC和ASSP应用面临越来越大的商业挑战

ASIC设计需要很长的时间投放市场、很高的前端资金投入以及大批量产出才能实现回报等,这些因素使得ASIC的投入风险非常大,只有很少的公司会承担这种风险。对于28 nm ASIC,ASIC工具模板和封装的流片(NRE)成本、知识产权(IP)许可以及物理设计服务等成本很容易超过1千万美元,在很多情况下,20 nm或者14 nm FPGA能够解决这些问题。相对于ASIC,虽然目前的FPGA需要严格的仿真验证,但是,与标准单元ASIC设计相比,实验室测试以及能够对FPGA重新编程等方法有效的降低了人工投入。FPGA组件价格虽然可能高于同样复杂的ASIC,但是应该考虑总体拥有成本。标准单元ASIC的收支平衡点在不断提高,前沿CMOS技术使得FPGA更复杂,性能更好,功耗更低,而这是ASIC难以实现的。

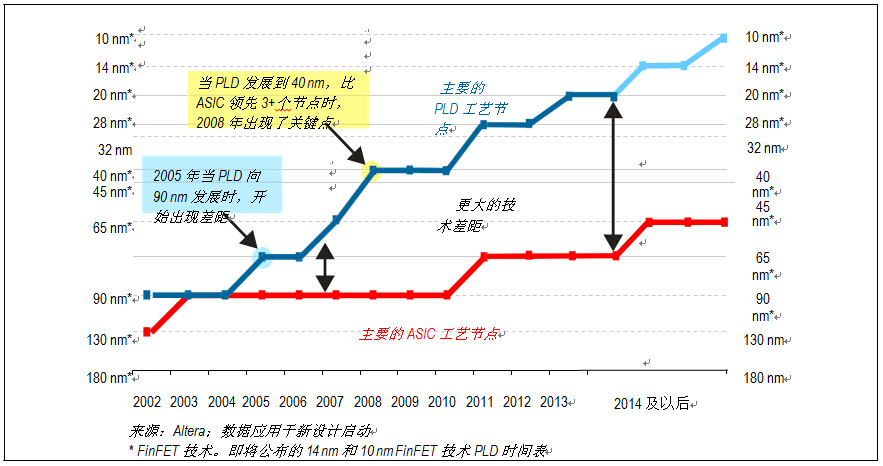

与FPGA和ASSP相比,低成本工艺节点会降低ASIC的优势,这是因为这些解决方案会把客户集中到更先进的工艺节点上,更具价格和性能竞争优势。目前的FPGA使用28 nm工艺,很快将采用20 nm以及更小的工艺技术。但是,大部分新ASIC设计要落后两到三个节点,甚至更多。差距越大,FPGA在价格、性能和集成度上就越具有吸引力。请参见图2。

图2.新设计的可编程逻辑和ASIC主要工艺节点对比

Gartner预测,到2016年,ASIC设计总数量每年会下降3.8%。而且,每过一年,每一设计都要求更高的产量才能获得收益(3)。只有大公司能够在市场上获得ASIC成本回报,对于大部分公司,ASSP和FPGA成为唯一的可行选择。

但是,ASSP价值地位也在下降,原因如下:

■ 提高处理器性能的挑战

■ 突出产品优势的需求

■ 响应市场的需求(产品及时面市)

■ 在可重新配置上不够灵活

硬件规划人员以前能够借助越来越高的处理器频率和越来越多的处理器内核来提高他们下一产品的系统性能。但是现在,由于处理器频率并没有随时间大幅度增长,而是通过增加处理器内核数量以实现并行工作,无法解决性能瓶颈问题,因此,硬件规划人员不能再采用这一方法来提高性能。很多硬件规划人员的解决方案是开发专用硬件,以解决这些软件瓶颈。

开发处理器使用的专用增强IP有助于解决这些难题。但是,竞争公司也可以使用让ASSP优于前一代产品的硬件加速功能。此外,无法通过使用ASSP来解决某些特殊软件的瓶颈。

ASSP的关键优势在于产品快速面市,但并不总是如此。需要ASSP特殊功能的小公司无法获得他们最需要的型号或何时将产品投放市场。大公司也得依靠供应商为他们提供所需要的产品。但是,他们能得到这些型号产品,其他公司也能得到。FPGA是克服这些ASIC和ASSP固有问题的好方法,在今后的产品中甚至能进一步增强功能。

评论