FIR滤波器原理

导读:FIR滤波器是非递归型滤波器的简称,又叫有限长单位冲激响应滤波器。在数字信号处理系统中较基本的元件,今天带大家了解FOR滤波器的原理

本文引用地址:http://www.amcfsurvey.com/article/275887.htm

FIR滤波器原理——特点

FIR滤波器有以下几点:

Ⅰ、数字滤波器还具有模拟滤波器不能比拟的可靠性。组成模拟滤波器的电子元件的电路特性会随着时间、温度、电压的变化而漂移,而数字电路就没有这种问题。只要在数字电路的工作环境下,数字滤波器就能够稳定可靠的工作。

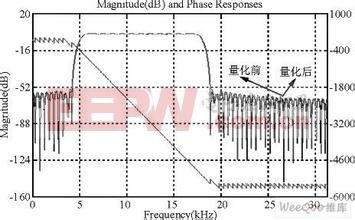

Ⅱ、数字滤波器相比模拟滤波器有更高的信噪比。这主要是因为数字滤波器是以数字器件执行运算,从而避免了模拟电路中噪声(如电阻热噪声)的影响。数字滤波器中主要的噪声源是在数字系统之前的模拟电路引入的电路噪声以及在数字系统输入端的模数转换过程中产生的量化噪声。这些噪声在数字系统的运算中可能会被放大,因此在设计数字滤波器时需要采用合适的结构,以降低输入噪声对系统性能的影响。

Ⅲ、数字滤波器的处理能力受到系统采样频率的限制。这是因为奈奎斯特采样定理,如果输入信号的频率分量包含超过滤波器1/2采样频率的分量时,数字滤波器因为数字系统的“混叠”而不能正常工作。如果超出1/2采样频率的频率分量不占主要地位,通常的解决办法是在模数转换电路之前放置一个低通滤波器(即抗混叠滤波器)将超过的高频成分滤除。否则就必须用模拟滤波器实现要求的功能。

数字滤波器具有比模拟滤波器更高的精度,甚至能够实现后者在理论上也无法达到的性能。

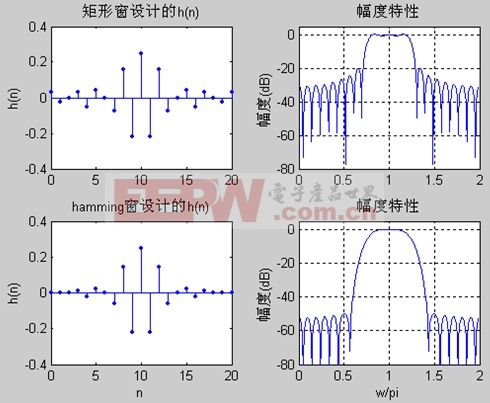

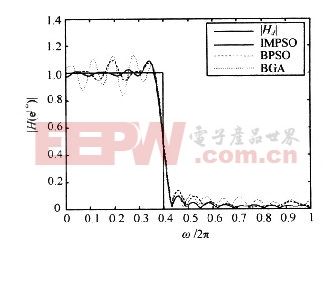

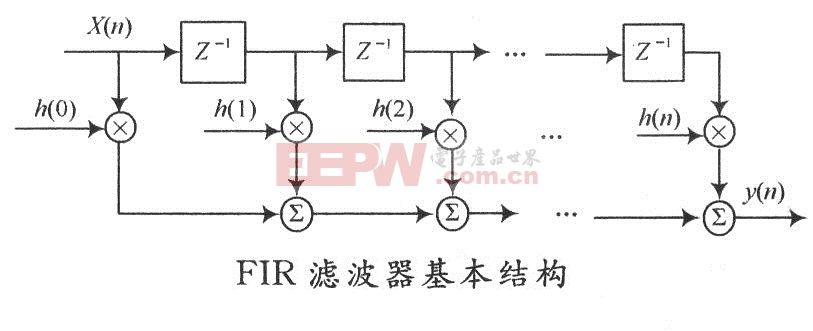

FIR滤波器原理——原理

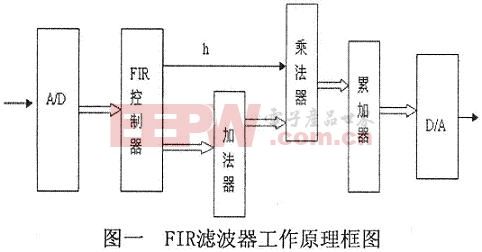

在信号进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不论采用乘累加方法还是分布式算法设计FIR滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

FIR滤波器原理——分类

FIR滤波器的在硬件上的分类有以下:分别是集成电路、DSP芯片、可编程三种。

集成电路:

一种是使用单片通用数字滤波器集成电路,这种电路使用简单,但是由于字长和阶数的规格较少,不易完全满足实际需要。虽然可采用多片扩展来满足要求,但会增加体积和功耗,因而在实际应用中受到限制。

DSP芯片:

DSP芯片有专用的数字信号处理函数可调用,或者根据芯片指令集的结构自行设计代码实现FIR的功能;由于FIR设计时其系数计算及其量化比较复杂,因此一般都采用MATLAB软件作为辅助设计,计算出FIR的系数;然后进行代码设计实现。实现FIR滤波器相对简单,但是由于程序顺序执行,速度受到限制。而且,就是同一公司的不同系统的DSP芯片,其编程指令也会有所不同,开发周期较长。

可编程:

FPGA/CPLD。FPGA有着规则的内部逻辑块阵列和丰富的连线资源,特别适合用于细粒度和高并行度结构的FIR滤波器的实现,相对于串行运算主导的通用DSP芯片来说,并行性和可扩展性都更好。

以下是FIR滤波器的一些文章,网友们可以参阅一下:

电路相关文章:电路分析基础

滤波器相关文章:滤波器原理

pic相关文章:pic是什么

滤波器相关文章:滤波器原理

低通滤波器相关文章:低通滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理

评论