LEON2应用于DCPU的FPGA仿真

0 引言

本文引用地址:http://www.amcfsurvey.com/article/273881.htm近年来,随着数字多媒体业务和Internet网络的迅速发展,新型数字机顶盒可以有效利用我国巨大的有线电视网络资源,完成视频点播、数字电视的接收及接入Internet等综合业务功能。

1 数字机顶盒总体设计方案

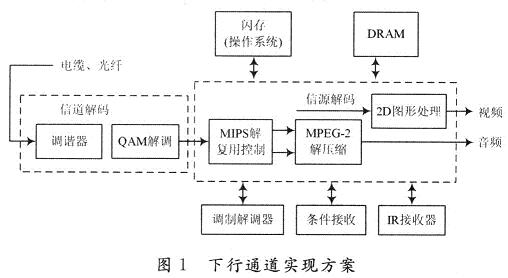

数字机顶盒分为两个通道,下行通道接收来自电缆或光纤的有线电视信号,上行通道传输从客户端到服务器端的指令。

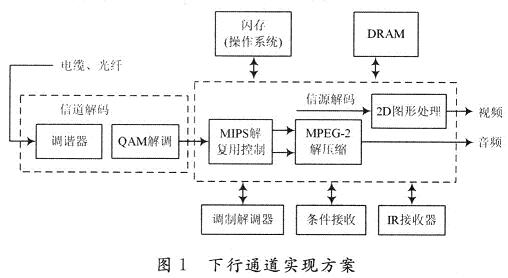

下行通道方案如图1所示,调谐器接收来自有线网的高频信号,通过QAM解调器完成信道解码,从载波中分离出包含音、视频和其他数据信息的传送流(TS)。传送流中一般包含多个音、视频流及一些数据信息。解复用器则用来区分不同的节目,提取相应的音、视频流和数据流,送入MPEG一2解码器和相应的解析软件,完成数字信息的还原。对于付费电视,条件接收模块对音、视频流实施解扰,并采用含有识别用户和进行记账功能的智能卡,保证合法用户正常收看。MPEG一2解码器完成音、视频信号的解压缩,经视频编码器和音频D/A变换,还原出模拟音、视频信号,在常规彩色电视机上显示高质量图像,并提供多声道立体声节目。

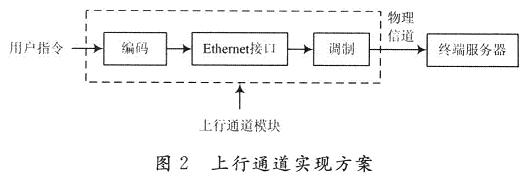

上行通道方案如图2所示,用户发送指令,然后经过编码符合网络通信协议,从以太网接口传输到调制器,再经物理信道传给终端服务器。

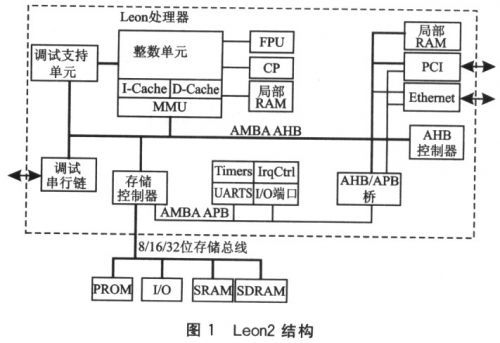

2 LEON2处理器

嵌入式CPU是数字电视机顶盒的心脏,当数据完成信道解码以后,首先要解复用,把传输流分成视频、音频,使视频、音频和数据分离开。CPU是嵌入式操作系统的运行平台,它要与操作系统一起完成网络管理,显示管理、有条件接收管理、图文电视解码、数据解码、视频信号的上下变换等功能。

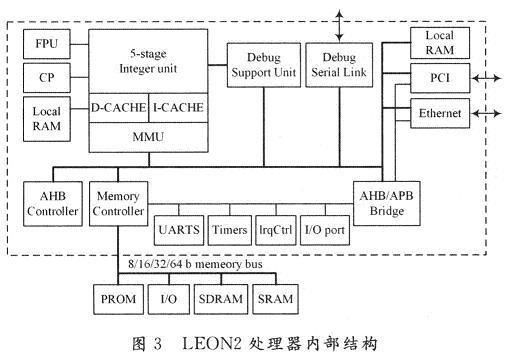

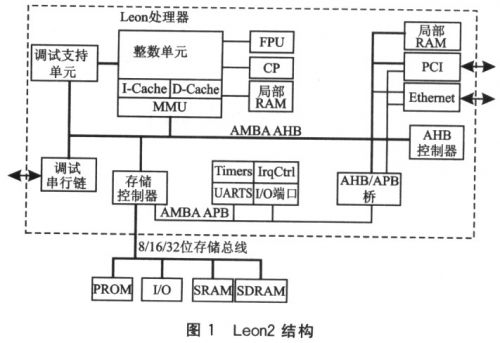

LEON系列32位RISC处理器核的第一个版本是LEONl,它是由欧洲航天局主持设计开发的。LEONl的设计初衷是为了使欧洲能够摆脱在航空航天高性能嵌入式处理器上对美国的严重依赖。以Jiri Caisler为首的设计团队在完成LEONl后从欧洲航天局独立出来,成立了Gaisler Research公司,后来就推出了LE—ON2处理器。LEON2是一个可配置的微处理器核,使用SPARC V8指令集,它的源代码由可综合的VHDL代码构成。LEON2内部结构如图3所示。

fpga相关文章:fpga是什么

评论