ICE时代正在悄然离去

硬件仿真是唯一一个可以部署在多个操作模式中的验证工具。事实上,它可应用于四个主要模式中,而且模式间的结合使用可以增加灵活性。基于以下两个特征对硬件仿真的应用模式进行分类:对映射到硬件仿真器中被测设计(DUT)的激励类型,以及DUT的响应过程。具体包括:

本文引用地址:http://www.amcfsurvey.com/article/273802.htm1.内电路硬件仿真(ICE)模式: 使用物理目标设备,通过频率适配器来驱动硬件仿真器中的DUT。

2. 基于事务的硬件仿真或加速模式: 使用虚拟目标设备,通过验证IP来驱动硬件仿真器中的DUT。

3. 软件仿真测试平台加速模式:通过程序语言界面(PLI)驱动硬件仿真器中DUT的寄存器传输级(RTL)测试平台。

4. 嵌入式软件加速模式:在硬件仿真器中的DUT处理器上执行软件代码。

将几种模式组合起来似乎是很有道理的,例如同时处理嵌入式软件及通过验证IP驱动DUT的虚拟测试平台。

纵观以往,ICE模式是最早提出的一种架构,这也是三十年前开始设计硬件仿真的原因。在ICE模式中,DUT映射到硬件仿真器内部,而硬件仿真器连接到由真实芯片组成的目标系统。

ICE具有两大关键优势。第一,目标系统可在DUT内外生成真实流量,从而在本质上取代了基于软件的传统测试平台。因此,无需创建测试平台,即可消除耗时又容易出错的工作,减轻验证工程团队因超负荷测试庞大设计所带来的负担。

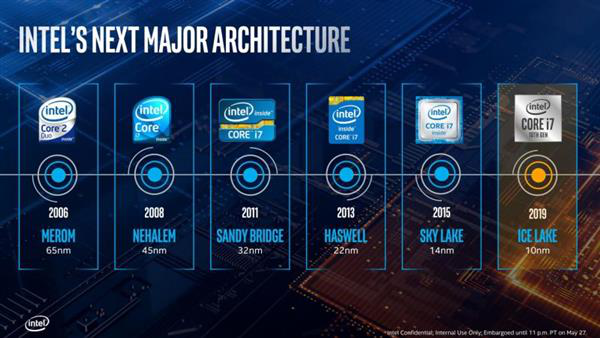

第二,能够以硬件仿真器的最大速度运行,较传统的硬件描述语言(HDL)软件仿真器而言,其速度提升了5~6个数量级。也就是兆赫与几十赫兹之间的差别。而现如今,其可能不再那么精确了。

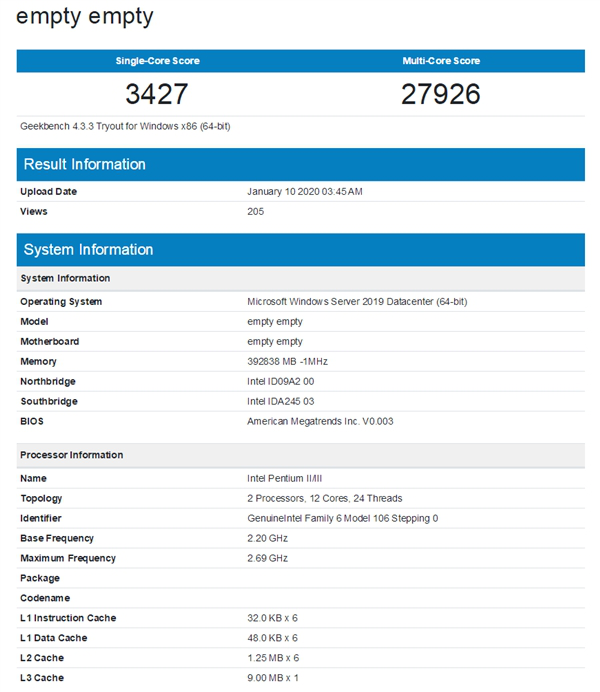

ICE模式存在诸多问题,有些已清楚明了,有些却还尚未明确。首先,无法直连目标系统,因为相较于硬件仿真器内部DUT的时钟,目标系统时钟的运行速度提高几个数量级,从而必须被限制到一或几兆赫。

为解决该问题,必须在目标系统与映射至硬件仿真器内部的DUT之间插入速度适配器——基本上就是一种基于先进先出(FIFO)寄存器的协议相关接口。它能够让目标系统的快速时钟适配硬件仿真器相对较慢的时钟速度。这种方法存在一些缺点,因为适配器通常会通过牺牲部分功能和准确性来换取性能。同时,PCI Express(PCIe) 或以太网等高速协议也将会减速,以应对适配器中FIFO内在容量的不足。

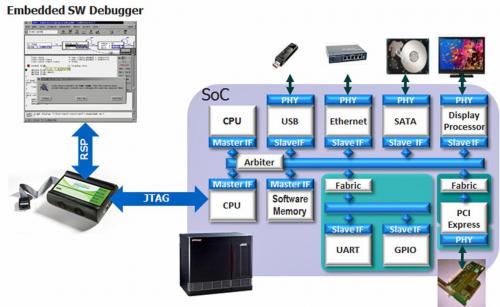

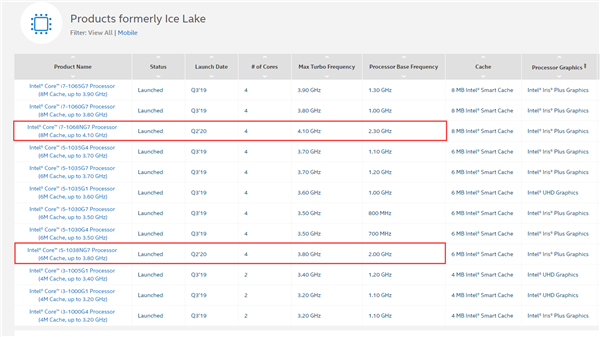

图1:带有多个物理接口的SoC通过速度适配器和实际外围设备进行建模。(由Mentor Graphics提供)

此外,适配器的周期精确行为由于同样的原因也将与实际协议有所不同。配置仅局限于每个协议一个测试用例,且不涉及边缘测试用例或任何“假设”分析。更不用说作为硬件的加速适配器针对电效应和磁效应所受到的影响。它们必须重置电路,需要磁屏蔽以及布设电缆和连接器,因为所有这些因素均可能影响其灵活性和可靠性。除此之外,相比软件解决方案,它们所能获得的利润率较低。

另一个明显的缺点就是在驱动DUT时,物理目标系统相对缺乏确定性行为或非重复性行为。多次运行同一测试时,其周期和时序可能会有所不同。也就是说,设计错误可能不会总在同一时刻出现。更糟糕的是,错误可能会完全不出现,影响问题的定位。此外,ICE模式无法实现物理目标执行保存和恢复的能力。硬件仿真只能保存 DUT 的状态,而非目标系统的状态。

然而,其最大的缺点就是它的极度不便性。如果没有人在现场提供帮助,对每个用户和设计相对应的速率适配器进行插拔,可能无法远程访问ICE模式的配置。

这一切均给ICE模式的使用带来麻烦,因而需要寻找其他替代方法。一种方法就是将物理测试环境变更为通过事务接口连接DUT的虚拟测试环境。这种部署模式通常称为基于事务的验证或TBX,由Mentor Graphics推广,适用于测试平台加速。

基于事务的验证

基于事务的验证并不是一个新概念,它在软件仿真领域已实践多年,主要受到生成复杂测试场景需求的驱动,旨在应对片上系统(SoC)不断攀升的复杂度。

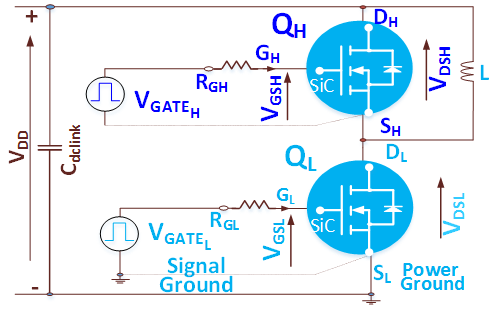

从概念上讲,这一构想十分简单。测试通过一种高级语言(例如SystemVerilog、SystemC或C++)从高抽象层次编写,并且从高级命令到位级信号的转换任务由一个叫做验证IP的专用实体执行(以下简称“验证IP”)。

一般来说验证IP包括可综合的用于实现接口协议的状态机功能模块。它可以使设计人员专注于创建复杂的测试平台,而无需理会讨厌的细节问题。通过将物理接口的抽象层次从周期/位级提升至事务层,验证IP可简化SoC 与其外围设备之间数据交换的描述。完成创建后,验证IP可重复使用。验证IP的示例包括一些通信协议,例如以太网、USB、PCIe、内存访问、JTAG端口,甚至是数码相机和LCD。

这一切听起来都不错,但却存在一个问题。此方法会产生大量测试周期,导致软件仿真器运行受阻。而软件仿真器仍然会通过验证IP执行从高级命令到位级信号的转换。运行分析器,然后发现测试平台所消耗的执行时间超过50%,甚至可能高达95%(其余时间由DUT消耗),这种情况并不少见。

硬件仿真平台必须得伸出援手,帮助提升频率性能,确保其速度不低于ICE。这是通过将验证IP的后端部分映射至硬件平台上实现的,而验证IP主要执行从高级命令到位级信号的转换。

以SystemVerilog、SystemC或C++等语言编写的测试平台会驱动验证IP的前端部分,进而提供比基于事务软件仿真快出5或6个数量级的执行速度。现在完全可以通过将一套速度适配器(以太网、PCI或USB)更换为对等的验证IP来构建一个虚拟的测试环境,从而取代ICE测试平台。

通过软件控制

与ICE不同,验证IP可从软件控制中受益。它可帮助智能验证环境实现高度灵活性并确保实现复用。例如,设计人员可以从动态主机中捕获和回放流量;通过转发设备与芯片之间的事务模拟内电路连接;或将转换应用于事务的数据流以实现难以获取的边缘测试用例。

相关实例:通过PCI验证IP,可将PCI软件驱动程序插入含有PCI接口的硬件仿真设计中,这与在ICE中通过硬件速度适配器的执行操作类似。但是现在,软件调试程序可以通过JTAG验证IP与硬件仿真器相连,并以单步模式运行,而通过JTAG物理连接却无法实现这一操作。

同样重要的是,当设计人员完全控制并非由硬件测试平台提供的设计时钟时,调试就变得更加轻松,也更加有效了。通过控制时钟频率,可以停止建模,读取内存内容,强制赋值寄存器或转储波形。

在ICE模式中调试需要硬件逻辑分析仪。如果使用ICE方法,设计人员就必须忍受真实硬件行为的突发状况,并且以牺牲可重复性为代价。相反,基于验证IP的虚拟测试环境可以帮助设计人员快速重现问题。此外,无需连结DUT与硬件测试平台,让设计人员在远程位置执行DUT,开启了通过远程访问创建仿真数据中心的大门。

由此看来,对于虚拟测试平台这一方法来说,创建测试平台似乎是唯一的一个缺点。而Mentor Graphics及其物理实验室VirtuaLAB(包括在工作站控制的软件中执行的所有外围设备)已成功解决这一问题。

虚拟设备

虚拟设备的功能与物理外围设备的功能相当,但虚拟设备不依赖于复位电路、电缆、连接器、磁屏蔽等硬件设备,也不会受到诸多麻烦的干扰。它们取决于全面的测试软件IP,该IP与嵌入到映射至仿真器上的DUT中的特定协议RTL设计IP进行通信。

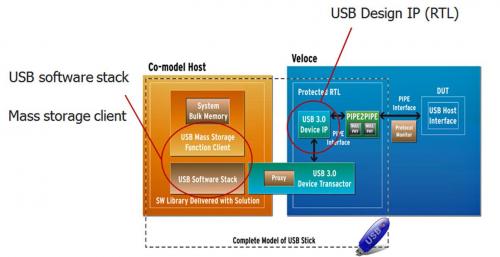

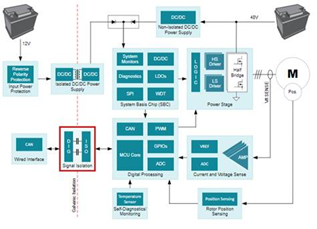

图2:虚拟设备将在控制工作站(协同建模主机)上运行的软件堆栈与通过TBX数据线在硬件仿真器上运行的通信协议IP组合起来。(由Mentor Graphics提供)

虚拟设备包括在工作站上运行的软件堆栈,该工作站通过TBX数据线与仿真器相连。整个封装可用于在设备级别上测试IP以及通过真实软件或设备驱动程序本身执行DUT验证。

与硬件ICE目标相比,虚拟设备的优势更为丰富:

轻松实现远程访问,无需安装连接到硬件仿真器的任何硬件设备。

自由灵活地在多个设计团队中共享单个硬件仿真器,无需配置用于连接的速度适配器和电缆。

在控制工作站上运行的目标协议软件堆栈清晰可见。

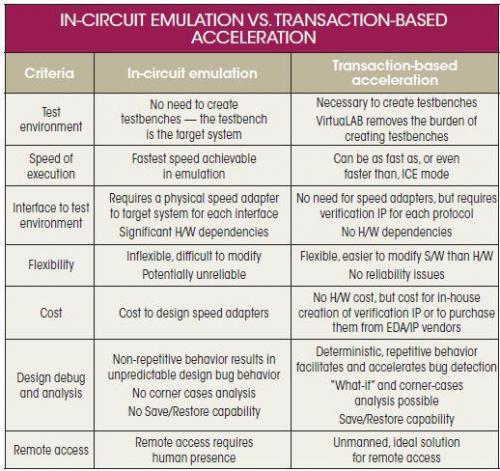

表1 总结了ICE的优点和缺点(相较于基于事务加速模式)。

然而,可能是出于习惯或者尚不知晓更好的替代方法,许多设计人员仍然沿用ICE模式。事实上,硬件仿真平台的所有供应商均声明支持ICE,虽然有些实现方案明显优于其他。然而,一旦设计人员通过硬件仿真体验了基于事务的验证方法,他们的验证观点就会有所转变。能够快速创建强大的测试环境而不受繁琐的ICE硬件的干扰,那么我们就可以更加轻松且更为有效地进行调试。这就是我认为ICE时代正在悄然离去的原因。

c++相关文章:c++教程

评论