FPGA系统设计的仿真验证之:SDRAM读写控制的实现与Modelsim仿真

(4)操作控制。

本文引用地址:http://www.amcfsurvey.com/article/273721.htmSDRAM 的具体控制命令由一些专用控制引脚和地址线辅助完成。CS、RAS、CAS 和WR 在时钟上升沿的状态决定具体操作动作,地址线和Bank选择控制线在部分操作动作中作为辅助参数输入。

由于特殊的存储结构,SDRAM 操作指令比较多,不像SRAM 一样只有简单的读写,具体操作指令如表7.3所示。

表7.3 SDRAM命令真值表

功 能命 令 字CSRASCASWEBAA10A[0:9]

取消器件选择DSELHXXXXXX

无操作NOPLHHHXXX

读操作READLHLHVLV

读等待/自动预充电READAPLHLHVHV

续表

功 能命 令 字CSRASCASWEBAA10A[0:9]

写操作WRITELHLLVLV

写等待/自动预充电WRITEAPLHLLVHV

Bank激活ACTLLHHVVV

对指定Bank预充电PRELLHLVLX

对所有Bank预充电PALLLLHLXHX

自动刷新CBRLLLHXXX

加载模式寄存器MRSLLLLVVV

由表7.3可以看到,虽然SDRAM的容量大、速度快,但是存在存储操作困难的问题。一般的解决方案有两种,一是直接控制SDRAM的读写时序实现数据的存储和读取,二是编写一个SDRAM的读写控制器,将SDRAM的读写简化成SRAM形式,通过几个命令完成SDRAM的读写。

3.SDRAM读写控制器

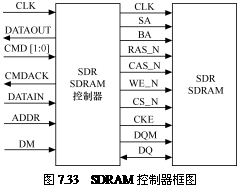

Xilinx、Altera、Lattice等较大的FPGA制造厂商都编写了自己的SDRAM接口控制器。读者可以到官方网站去申请相关的控制器源代码。下面简单介绍其中一种,如图7.33所示是该SDRAM控制器总体设计框图和外部接口信号。

在图7.33中,控制器右端接口信号均为直接与SDRAM 对应管脚相连的信号,在表7.2中已做介绍,不再重复。

控制器左端的接口信号为与FPGA 相连的系统控制接口信号,定义如下。

· CLK:系统时钟信号。

· ADDR:系统给出的SDRAM 地址信号。

· DATAIN:系统用于写入SDRAM 的数据信号。

· DATAOUT:系统用于从SDRAM读出的数据信号。

· CMD[1:0]、CMDACK:系统和控制器的命令交互信号,参见表7.3。

· DM:数据Mask信号。

一般来说,SDRAM的读写控制时序可以分为初始化、写寄存器、自动刷新、突发模式读、突发模式写、整页读以及整页写等主要操作。具体的时序图可以查阅相关的器件数据手册,这里不再列出。

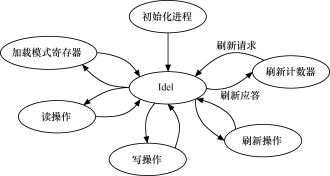

SDRAM的读写控制也可以由如图7.34所示的读写状态机表示。

在FPGA中,实现如图7.34所示的状态机,再利用已有的SDR SDRAM控制器即可实现对SDRAM器件的控制。

图7.34 SDRAM读写状态机

7.6.3 SDRAM控制器的Modelsim仿真

(1)打开ModelSim软件。

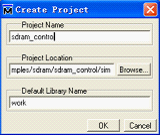

(2)创建工程。

如图7.35所示,在Modelsim中创建新工程,并设置工程的相关属性。

图7.35 创建工程

(3)添加设计输入。

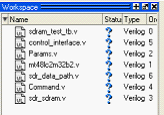

若要创建新的文件就选择【Create New File】图标,若要添加已经存在的文件就选择【Add Existing File】图标,如图7.36所示。本实例中使用已经存在的SDRAM控制器源文件作为设计输入,添加后,在Workspace浏览器中可以看到如图7.37的设计输入列表。

图7.36 添加设计输入 图7.37 SDRAM设计输入列表

(4)编译设计输入。

如图7.38所示,在任意一个源文件上单击右键,选择“Compile”/“Compile All”,对所有的源文件进行编译。

编译后,若有错误,Modelsim会在信息栏中显示出来。这时只要双击该错误,ModelSim就会自动打开该错误所在的文件,并定位到出现错误所在的位置附近。若编译正确通过,源文件后面的蓝色问号就替换成为绿色的对号,如图7.39所示。

评论