接收机的中频处理技术

摘要:本文对数字中频信号处理技术进行了研究,采用软件无线电的设计思想和解决方案,提出了一种基于“AD+FPGA”的中频信号处理技术,在频谱分析仪及信号分析仪等接收机中应用广泛。

引言

随着数字技术的发展,接收机的设计越来越多地采用软件无线电(software radio)的思想,以开放性、可扩展、结构精简的硬件为通用平台,把尽量多的功能用可重构、可升级的构件化软件来实现。从实际设计来说,射频模块尽量简化,将信号通过ADC转换为数字信号进行处理,提高接收机的稳定性、通用性并降低实现成本。在接收机中,最常用的是频谱分析和信号分析功能,本文以现场可编程逻辑器件(FPGA)为设计基础,简述频谱分析和信号分析的中频处理。

1 方案

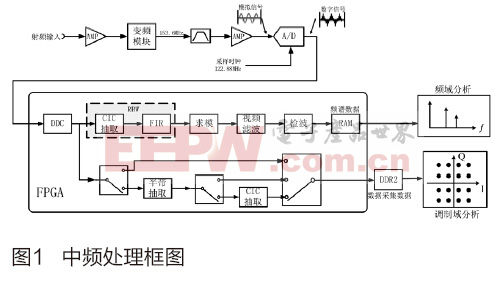

输入的射频信号经过变频模块生成153.6MHz的中频信号,通过ADC进行122.88MHz频率采样,数字信号送入FPGA进行数字下变频(DDC)、CIC抽取、RBW滤波、求模、视频滤波、检波后存入RAM后送CPU进行频谱分析;经过DDC、半带滤波及CIC后存入DDR2后送CPU进行信号分析,包括矢量信号解调,GSM、TD-SCDMA、WCDMA、TD-LTE及FDD-LTE分析等通信制式的非信令解调。具体中频处理框图如图1所示。

2 具体实现

2.1 模数转换(AD)

ADC是整个中频处理的关键部分,它直接关系到整个接收机的性能指标,其选用主要参考二个指示,即信噪比和采样频率。由于信噪比与ADC的有效位数有直接关系:SNR=(6.02N+1.76)dB,其中N为ADC的位数,所以尽量选用高位数ADC;同时,由于中频的宽带化需求,需要高采样时钟的ADC,如要满足40MHz的分析带宽,理论上要求采样时钟大于80MHz,本设计的采样时钟为122.88MHz。综合两方面考虑,ADC我们选用了LINERA公司的LTM9001。

2.2 数字下变频

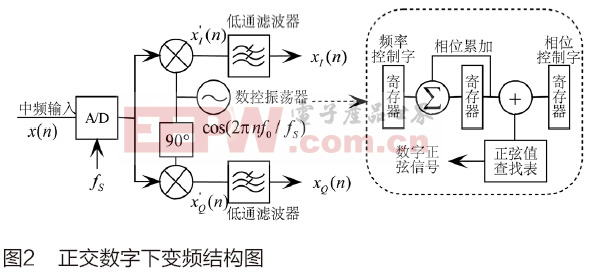

数字下变频(DDC)是数字接收机中的关键技术,广泛应用于雷达、声纳和无线电接收机中,主要将中频信号混频到基带,便于后续处理。它跟模拟下变频类似,包括数字混频器、数字控制振荡器及数字低通滤波器三部分,基本结构图见图2所示。

在本设计中,由于fo=153.6MHz,fs=122.88MHz,满足fo/ fs =(2n+1)/4,NCO输出为cos(0)、cos(π/2)、cos(π)、cos(3π/4),即1,0,-1,0等几个特殊值,实现了免混频,用简单的组合逻辑和取反电路就能实现,具体方法为:先将输入信号每隔2 个取2 补码,形成一个新的数据流;再将新数据流每隔一个置0,所得输出就是混频后的信号。

2.3 CIC抽取滤波

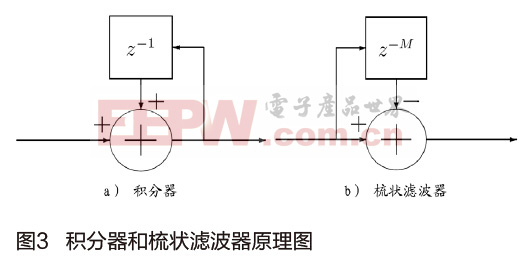

在数据处理系统中,经常需要将信号的采样率降低以便其后进行数字处理或存储,接收机最常用的是CIC抽取滤波或半带抽取滤波。CIC滤波器是级联积分梳状滤波器(Cascaded Integrator-Comb Filter)的简称,其基本构成单元是积分器和梳状滤波器。经过若干级级联后可实现采样率整数倍的抽取和内插,在接收机的设计中,主要采用CIC进行抽取。抽取滤波器可以实现降低取样速率并能使通带混叠或误差依据在要求的范围之内。积分器和梳状滤波器的原理图如图3所示。

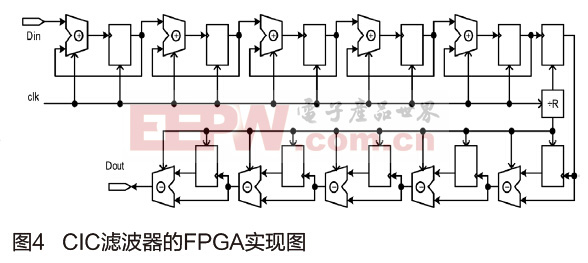

在滤波器的实现时,CIC将只有加法而没有乘法,有效地节省了硬件资源。其FPGA实现框图及其控制时序图如下,只需通过改变抽取率R值,就可以实现大范围整数倍抽取。

2.4 RBW

信号经CIC滤波器抽取后降低了率采样速率,但频谱分析仪需要实现从1Hz~3MHz的分辨率带宽,此时,为了得到更高质量的频谱波形,需要添加高斯FIR滤波,这里RBW大于等于1kHz时选择了25级、22 bit滤波器系数,RBW小于1kHz时选择了1024级,22 bit滤波器系数,满足带外衰减优于100 dB。

2.5 半带滤波抽取

半带滤波器(Half-Band Filter)在多速率信号处理中有着特别重要的位置,半带FIR滤波器系数对称、约一半的系数为零,可节约FPGA的MAC资源,是一种高效的数字滤波器。因此这种滤波器特别适合实现![]() (即2的幂次方倍)的抽取或内插,而且计算效率高,实时性强。

(即2的幂次方倍)的抽取或内插,而且计算效率高,实时性强。

图5采用半带抽取方式实现降低信号采样速率的要求。假设有N级半带滤波器实现抽取,FS0是输入采样速率,FSN是第N级半带滤波器的输入采样速率,则FSN= FS0/2N,且信号经过每一级半带滤波器抽取后,带宽变为原来的一半。半带滤波和CIC抽取滤波结合降低信号的采样率,实现大跨度码元速率信号的处理。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

低通滤波器相关文章:低通滤波器原理

电源滤波器相关文章:电源滤波器原理

混频器相关文章:混频器原理 矢量控制相关文章:矢量控制原理 数字滤波器相关文章:数字滤波器原理 汽车防盗机相关文章:汽车防盗机原理 频谱分析仪相关文章:频谱分析仪原理

评论