基于FPGA的DDR3多端口读写存储管理系统设计

机载视频图形显示系统主要实现2D图形的绘制,构成各种飞行参数画面,同时叠加实时的外景视频。由于FPGA具有强大逻辑资源、丰富IP核等优点,基于FPGA的嵌入式系统架构是机载视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。

本文引用地址:http://www.amcfsurvey.com/article/271735.htm与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此选择DDR3 SDRAM作为机载视频图形显示系统的外部存储器。

本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。

1总体架构设计

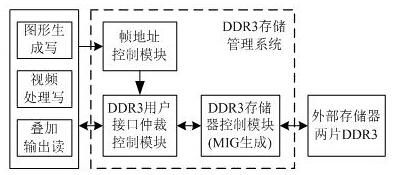

机载视频图形显示系统中,为了实现多端口对DDR3的读写访问,设计的DDR3存储管理系统如图1所示。主要包括DDR3存储器控制模块、DDR3用户接口仲裁控制模块和帧地址控制模块。

图1 DDR3存储系统设计框图

DDR3存储器控制模块采用MIG(Memory Interface Generator)方案,通过用户接口建立FPGA内部控制逻辑到DDR3的连接,用户不需要管理DDR3初始化、寄存器配置等复杂的控制逻辑,只需要控制用户接口的读写操作。

DDR3用户接口仲裁控制模块将每一个数据读写请求设置成中断,借鉴中断处理思想来进行仲裁控制,从而解决数据存储的冲突。

帧地址控制模块控制帧地址的切换。为了提高并行处理的速度,简化数据读写冲突,将图形数据和视频数据分别存储在不同的DDR3中。

2 DDR3存储器控制模块设计

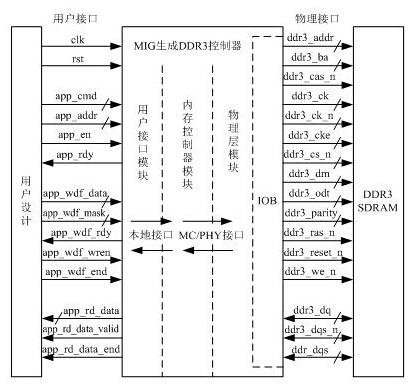

MIG生成的DDR3控制器的逻辑框图如图2所示,只需要通过用户接口信号就能完成DDR3读写操作,大大简化了DDR3的设计复杂度。

图2 DDR3控制器的逻辑框图

2.1 DDR3控制模块用户接口写操作设计

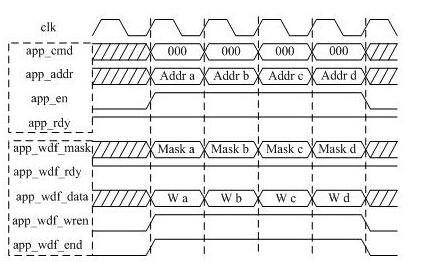

DDR3存储器控制模块用户接口写操作有两套系统,一套是地址系统,一套是数据系统。

地址系统的内容是app_addr和app_cmd,两者对齐绑定,app_cmd为000时为写命令,当app_rdy(DDR3控制)和app_en(用户控制)同时拉高时,将app_addr和app_cmd写到相应FIFO中。数据系统的内容是app_wdf_data,它在app_wdf_rdy(DDR3控制)和app_wdf_wren(用户控制)同时拉高时,将写数据存到写FIFO.

为了简化设计,本文设计的用户接口写操作时序如图3所示,使两套系统在时序上完全对齐。

图3 DDR3写操作时序图

2.2 DDR3控制模块用户接口读操作设计

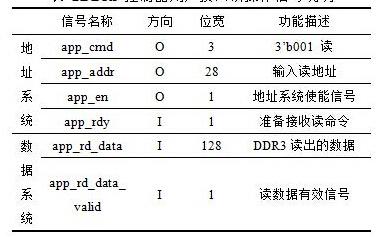

用户接口读操作也分为地址系统和数据系统。用户接口读操作信号说明如表1所示。

表1 DDR3 控制器用户接口读操作信号说明

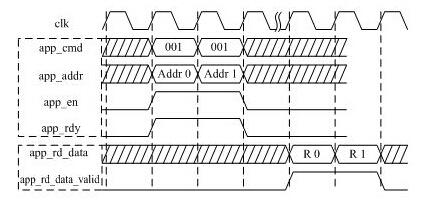

地址系统与写操作相同,在时钟上升沿且app_rdy为高电平时,用户端口同时发出读命令(app_cmd=001)和读地址,并将app_en拉高,将读命令和地址写到FIFO中。对于数据系统,当app_rd_data_valid有效,则读数据有效,读回的数据顺序与地址/控制总线请求命令的顺序相同。

读操作地址系统和数据系统一般是不对齐的,因为地址系统发送到DDR3后,DDR3需要一定的反应时间,读操作时序如图4所示。

图4 DDR3 读操作时序图

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论