用FPGA来加速采用OpenCL的多功能打印机图像处理

D. TRC调整

本文引用地址:http://www.amcfsurvey.com/article/271266.htmTRC调整算法是一个简单的LUT.它允许C、M、Y、K值的进一步调整,以校正非线性色调再现。具体C、M、Y、K LUT条目凭经验来测量。

E.误差扩散

最后阶段执行半色调功能。彩色激光MFP产品使用一个激光系统来消除感光介质上的电荷。无论电荷清除的是C、M、Y、K,墨粉都不能转移到感光体。激光束扫过移动的感光体,被调制来创建一个倒置的图像。调制的最小时间周期是一个像素。在反转图像被写入感光体后,它经过一个墨粉分配器附近。然后,带有相反电荷的墨粉被吸引到电荷存在的感光区。墨粉“粘”到感光体上。最后一个步骤是将感光体上的图像转印到纸张或其他介质上。单个像素或开或关,实现二进制的1过程。来自TRC内核的8位CMYK像素必须半色调或二进制化,以驱动打印机中的激光系统。有许多算法可以将连续色调数据转换为二进制数据。误差扩散是MFP/打印机中使用的一种通用算法。我们选择了实施众所周知的弗洛伊德-斯坦伯格(Floyd-Steinberg)误差扩散算法的一个变种,它有简单的算术修正系数[7].

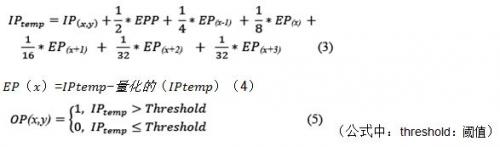

弗洛伊德-斯坦伯格误差扩散量化了基于一个阈值阵列的输入像素,然后将剩余误差分配到相邻像素。在我们的案例中,我们将一个8位输入像素减少到二进制输出像素。因此,我们的阈值阵列是一个127的值。大于127的输入像素成为了逻辑1.≤127的像素成为了0.该算法定义如下:

1. IP(x,y)是当前输入像素

2. EPP是来自以前像素的剩余阈值误差,IP(x-1,y)

3. EP是来自以前扫描线的误差矢量,y-1.

VII.扩展和增强

A.扩展CCP到整个系统

下一步骤是采用CCP并将其连接到数据输入的扫描装置和数据输出的打印装置。这将需要增加一个校准内核和简单的CST将RGB转换为L*a*b*.根据在扫描设备中使用的传感器阵列类型,即电荷耦合器件或接触式图像传感器,红、绿和蓝行数据可能无法在垂直方向对准。行数据的对准可能需要几十行缓冲区,这在FPGA内存资源方面是非常昂贵的。为了缓解这一问题,原始RGB数据将使用DMA暂时保存在HPS内存中。然后,红、绿、蓝、行数据的对准可以使用DMA指针和偏移来完成。然后校准对准的RGB数据,并通过通道传递到基本CST内核。

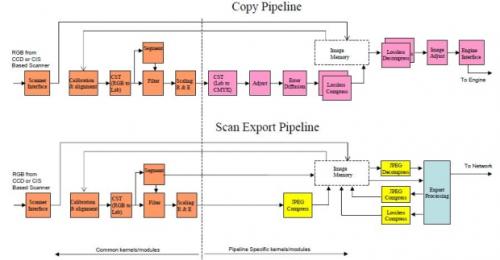

基本CST内核将依次使用通道直接将数据传递到滤波器输入模块。我们的期望是,这些额外内核将适合未使用的逻辑和内存资源。图22显示了完整的复印流水线。请注意,除了有全扫描仪接口的CCP,分割、无损压缩模块和引擎级都不适合Cyclone V SoC器件。完整的图像路径将需要更大型的FPGA.

B. ARM内核和NEON协处理

除了FPGA架构和OpenCL,Altera SoC系列器件还采用了双核ARM Cortex A9内核和NEON协处理器。图像处理流水线的某些模块可以卸载到CPU.在分割操作和完成压缩/解压缩功能的特定部分可以使用NEON提供的有SIMD加速的CPU来完成。

C.动态FPGA可重编程性

Altera SoC FPGA提供的动态重新配置允许用户重新编程FPGA架构,同时CPU运算继续运行。这个特点在MFP中特别有用,而其中的一些操作永远不可能同时发生。例如,扫描和复印操作共享6个共同输入功能,如图22所示。其余的复印操作、CST压缩,以及剩下的扫描输入功能、JPEG压缩将永远不会同时运行。因此,我们可以创建两套内核,其中包括共同的扫描仪功能和多种后端功能。这些流水线可以在给定所需时间基于MFP操作来动态加载。在一个传统ASIC中,这些模块和数据通路都必须包括在内。动态图像路径的重新配置可以实现更小的FPGA,从而实现更低成本的图像路径。

D. Arria V和Arria 10 SoC

Altera的Arria V和最近发布的Arria10 SoC为功能齐全的MFP图像路径解决方案提供了一个可扩展平台。增加的内存、更快的时钟速度,加上更高性能ARM内核的大型FPGA架构为图像处理和一般计算要求提供了完整解决方案。

图:完整的复印和扫描流水线

图字:

复印流水线

来自CCD或基于CIS扫描仪的RGB;分割;图像内存;无损解压缩;图像调整;引擎接口

扫描仪接口;校准和调整;CST(RGB到Lab);滤波器;缩放R E;CST(Lab到CMYK);调整;误差扩散;无损压缩;至引擎

扫描出口流水线

来自CCD或基于CIS扫描仪的RGB;分割;图像内存;JGEG解压缩;至网络

扫描仪接口;校准和调整;CST(RGB到Lab);滤波器;缩放R E;JGEG压缩;JGEG压缩;出口处理;无损压缩

通用内核/模块;流水线特定内核/模块

VIII.总结和结论

OpenCL和Altera的工具链有助于2名全职OpenCL软件工程师、1名全职硬件工程师和其他兼职人员的一个小型团队在约4.5个月内实现CCP.团队可从C语言算法开始,创建一个高水平的基于C语言的CCP图像流水线,将算法移植到OpenCL,在x86平台上测试OpenCL以验证基本功能,增加厂商特定扩展,学会Altera OpenCL工具流程,最后在Altera的参考平台上测试结果。团队还可开发一个测试环境来验证位级别OpenCL结果的正确性。此外,团队可创建一个基于Web的应用,允许用户选择源图像,通过一个基于C语言的CCP和OpenCL加速的CCP运行图像,显示半色调图像,并提供计时结果。软件工程师可以没有以往的FPGA经验,硬件工程师也可以没有以往的OpenCL经验。

这种新模式演示了一个小型团队如何可以快速从一组算法到全面功能,优化以硬件实现的流水线。大约50%的开发时间专注于优化,包括最大限度地提高性能和最大限度地减少FPGA资源利用。该团队预计,后续项目开发时间可减少50%。

MFP厂商不再需要投入数百万美元和多年时间来开发ASIC或SoC.OpenCL和Altera SoC器件提供了一种在最短时间内实现高性能、低成本MFP控制器的新模式。

fpga相关文章:fpga是什么

三维扫描仪相关文章:三维扫描仪原理

评论