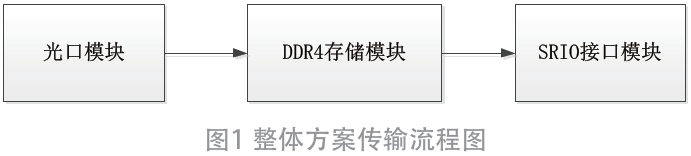

引进CRC/3DS架构 DDR4数据传输性能/可靠度跃升

相较前一代记忆体规格,第四代双倍资料率(DDR4)新增超过二十种功能,其中,采用循环冗余校验码(CRC)和立体矽堆叠(3DS)技术更是重大变革,前者可即时检测资料汇流排上的错误讯息,提升可靠度;后者对提升时序和功率效能则大有帮助。

本文引用地址:http://www.amcfsurvey.com/article/269343.htm随着标准不断演进,新一代记忆体规范通常着重于提升资料传输速率,其他方面仅略做调整,但第四代双倍资料率(DDR4)并非如此。DDR4首次亮相时,便新增超过二十种功能,比先前DDR规格足足多一倍。

前几代的DDR规格创新,主要目标是提供更快速度或更广泛的应用,然而,为使低耗能效益持续有所改善,DDR产品须进行更大的设计变革;新一代的DDR4不仅提高速度,也拓展市场广度,以下列举几项DDR4的重大变革。

新增CRC验证机制 DDR4可检测资料汇流排错误

首先,DDR4在可靠性和制造技术方面都大幅改进,让DDR测试变得更方便。举例来说,DDR4新增写入资料时的循环冗余校验码(Cyclic Redundancy Check, CRC),可即时检测资料汇流排上的错误讯息,一旦发现CRC错误,且写入资料被删除,便很可能是读取错误。然而,在汇流排上进行CRC运算验证,将能在传输资料时检测错误讯息,这对资料写入和非除错Non-ECC记忆体应用有很大的帮助。

另外,当动态随机存取记忆体(DRAM)侦测到 CRC错误,如很短的低电压脉冲,它会将ALERT_n值标记为低值(Low),并将CRC错误标志MR5,以及CRC错误状态MPR设定为1;接着,在 CRC错误被删除之前,MR5必须重设为0,或将其清除;由于CRC错误和C/A奇偶校验错误会产生相同错误代码,即ALERT_n LOW,因此,如何判断错误类型,有赖于联合电子设备工程委员会(JEDEC)所提出的解决之道。

透过JEDEC的解决方案,设计工程师可由错误持续的时间长度,来分辨产生的究竟是哪种错误。若低值持续六至十个时脉周期,是CRC错误;如果持续了四十八至一百四十四个时脉周期,则为C/A 奇偶校验错误。透过C/A奇偶校验功能,可让工程师以低成本方式,进而确认链路上的指令和位址汇流排对称性。

善用状态分析 DDR4除错效率大增

DDR4的最大挑战,或许是如何在DIMM/SODIMM插槽上进行方便探量。由于DDR4采球栅阵列(BGA)封装,导致DDR3跟DDR4使用不同的DIMM及SODIMM插槽,因此,DDR4需要全新的探量方式。

然而,随着资料传输速率提升和电压下降,资料有效窗口变得更小,当资料有效窗口变小,临界值设定便成为有效量测时脉与时序模式的关键要素;时序模式是逻辑分析仪最基本的模式,可告知事件发生时间,并可对逻辑分析仪的内部时脉进行取样;不过,时序模式与DDR4系统不同步,因此只能提供有限的系统讯号流量资讯。

此外,状态分析同步,代表取样时脉来自待测装置(DUT)。而状态分析的目的是为了检查发生状况,用户可藉由追踪汇流排上的数值来得到所需资讯,透过这种方式,用户得以监控码流,快速找出功能问题。事实上,状态分析能够和待测装置一样看到DDR4指令、位址、资料与系统时脉之间的关系,实是准确检视DDR4活动的关键。

状态模式通常用于软体除错,以确保记忆体控制器和DRAM之正常运作。进行硬体除错和软硬体整合时,如果难以确定错误发生位置,也可使用状态模式;常来自待测装置的时脉产生后,工程师须进行准确的同步取样,如此能有助系统运作在错误出现时撷取资料。

不过,如欲准确撷取汇流排中的资料,逻辑分析仪的设定/保持时间(Setup/Hold Time)须短于资料有效窗口,系因资料有效窗口与汇流排时脉相对应的位置,会因不同类型的汇流排而异。而在DDR4速率下,准确撷取资料有效窗口变得更为复杂,其原因来自逻辑分析仪可用资料的有效窗口不断缩小,但利用该状态模式,可让使用者藉由监控码流,以及追踪汇流排上的数值,快速找出错误。

DDR4亦须发展新的交流参数测试方法。DDR4比DDR1快近五十倍,要达到这个速度,唯一方法是改变交流时序规格,然而更大的效能意味着更多重新设计,使产品符合严格规范的同时,也造成产品延迟进入市场、售价变得更高,这种情况自然没有任何记忆体公司乐见。

采行3DS架构 DDR4提升时序/传输效能

幸好DDR4藉由改变规格,沿用DDR3系统设计和时序策略以解决这些问题。事实上,所有DDR4规格的变化其实都隐含立体矽堆叠(3DS)的概念,在传统堆叠中,DRAM堆叠是为了减少整体电路所需的涂料,但在DDR4的高速下,传统堆叠有局限性;立体矽堆叠可增加密度,其架构由一个主要DRAM和多达八个从属的DRAM堆叠组成,甚至还能在单一载点上安装多达八个元件。

主DRAM也为从属DRAM提供屏障,让电力负荷维持在单一节点。由于3DS的阶级选取(Rank Selection)均经过编码,因此使用者能更有效率地使用接脚。同时3DS具有独特的单模暂存器介面,许多指令比如重设,其可同时广播给所有 DRAM;其他指令则仍然个别发送给不同DRAM,这些指令包括启动、读出、写入、预充电和刷新等。

DDR4改用立体矽堆叠,对提升时序和功率效能有很大帮助,不仅让用户工作效率大增,同时也满足突破性速度的需求。

评论