FPGA设计开发软件ISE使用技巧之:增量式设计(Incremental Design)技巧

6.6 增量式设计(Incremental Design)技巧

本文引用地址:http://www.amcfsurvey.com/article/269337.htm本节将对ISE下增量式设计做一个全面的介绍。FPGA作为一种现场可编程逻辑器件,其现场可重编程特性能够提高调试速度。每次硬件工程师可以很方便地改变设计,重新进行综合、实现、布局布线,并对整个设计重新编程。

然而当设计算法比较复杂时,每一次综合、实现、布局布线需要花很长的时间。即使仅仅改变设计中的一点,也会使综合编译的时间成倍增加。而且更为麻烦的是如果整个工程的运行频率很高,对时序的要求也很严格,这样重新布线往往会造成整个时序错乱。

运用增量式设计可以有效地解决这一问题。一方面大大节约综合、布局布线的耗时,另一方面可以继承前一设计中已有的成果,是一种比较常用的设计流程。

6.6.1 增量式设计的必要性

增量式设计(Incremental Design)方法是一种能在小范围改动情况下节约综合、实现时间并继承以往设计成果的设计手段。作为一个流程,增量设计能够极大地减小布局布线时间,并且当对一个近似完整的设计作小的变动,可以保持整个系统的性能。

在增量设计中每一个逻辑分组在Xilinx的FPGA里受到约束以使之只占有自己的空间。在设计中,对当对其中之一的逻辑分组做改动时,一个增量设计流程可以确保未做改动的逻辑分组在进行综合输出时不变化。接着布线工具对改动了的逻辑分组重新进行布局布线,而未改动的逻辑分组则继续以前的布局布线结果,这使得整个设计的布局布线时间得以削减。

增量式设计对一处复杂的设计来说是非常必要的,主要是因为增量式设计有以下两个方面的优点。

1.减小综合、布局布线的耗时

当仅对大型设计工程的局部进行改动时,增量设计流程仅仅改动的部分重新编译,如果改动模块的接口设计恰当,将不会影响其余部分的综合与实现结果,布局布线时也只对改动部分重新布线,未改动的部分保持不变,从而节约了整个编译、布局布线与优化的耗时。

2.能够很好地继承未修改区域的实现成果

这一点对于对时序要求很严格的设计来说是很有用的。如果一个设计经过多次调试,附加合适的约束,设置恰当的参数达到了最佳实现成果。但是因为对某个细节进行了修改,就需要全部重新综合、布局布线,这样可能前面所做的精心调整工作都无效了。

通过增量式设计,可以解决这一问题。对于已达到设计要求的部分将其保持不变,仅对修改的部分重新编译、布局布线,从而保证在最大程度上继承以往的实现结果。

6.6.2 增量设计流程

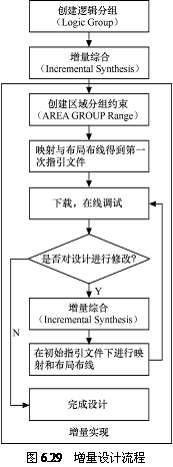

具体的增量设计流程如图6.29所示。

增量设计的流程可归纳如下。

1.创建逻辑分组(Create Logic Group)

在增量设计中为了实现减小综合、布局布线耗时,极大程度地继承未修改区域的成果,必须要求将设计分成多个逻辑分组。每个逻辑分组应该分配一定的逻辑区域,当某一逻辑分组的内容发生改变时,增量设计可以在该逻辑分组分配的逻辑区域内对其进行重新综合和布局布线,而不会影响到其他的逻辑分组。

所谓“逻辑分组”,是惟一的逻辑层次中的若干逻辑实体的划分。比如在顶层逻辑层次中每个子模块即为一个逻辑分组。在代码中即为顶层中“module(Verilog)”和“entity(VHDL)”定义的子模块的实体。在一个设计中往往将实现的不同功能设置为不同的模块,然后在一个顶层模块中实例化所有这些不同功能的模块,从而实现一个完整的功能,那么这些不同功能的模块就可以看作是不同的逻辑分组。

在进行逻辑分组时,需要考虑以下因素。

(1)设计中所有逻辑除了IOB和时钟逻辑,都应该包含在逻辑分组当中。

(2)顶层模块不应该包含复杂逻辑,仅仅包含一些I/O定义、时钟分配逻辑和所有子模块的实例化,直正的功能实体用子模块的逻辑描述。增量设计方法希望将所有的逻辑实体分割到子模块中去,而顶层模块不含任何实际的逻辑功能,以便于做相应的区域约束。

顶层包含实际逻辑功能的缺点在于:当顶层改变时,相关的Logic Group的接口将发生变化,从而影响Logic Group的结构,在做编译和布局布线时,会影响增量设计的效能。

(3)逻辑模块分组必须以寄存器输出,即用寄存器分割模块。这一点其实不仅仅是增量设计的需求,也是合理划分模块的一个基本要求。

如果采用同步时序方式设计电路,用寄存器分割逻辑模块,模块间的接口尽量简单,则时序优化路径集中在同一模块内部而不是模块之间的边界上。这样能够使综合器完整地掌握需要时序优化的路径,从而避免了因一个模块内部改变而通过边界影响到其他模块的时序这种不利于增量设计的情况发生。

(4)每个逻辑分组为其附加区域分组约束。

2.增量综合(Incremental Synthesis)

所谓增量综合是指只有改变的部分重新综合,而对未改变部分保持原有的综合结果的一种综合技术。传统的综合技术即使有微小的改动,也会对整个设计重新综合。

如果要实现增量综合必须对综合工具做相应的设置。在这里主要讲述ISE自带综合工具XST是如何实现增量综合的,对于其他综合工具如:Synplify/Synplify Pro和Leonardo Spectrum综合工具,在这里不做详细介绍。

XST支持单一工程的模块级增量综合(BLSI)。实现的方法为在XST的约束文件(扩展名为xcf)中附加逻辑分组约束,从而告知XST Logic Group的边界。

XST在综合时,所有的编译与优化都不超越用户在XCF文件中约定的Logic Group的边界,以达到在细微修改后仅仅对Logic Group内部进行重新综合的目的。这样一个逻辑分组HDL源代码的改变就不会对其他逻辑分组造成影响。

fpga相关文章:fpga是什么

评论