基于OV6630图像传感器和DSP的图像采集系统设计

0 引言

本文引用地址:http://www.amcfsurvey.com/article/268279.htmDSP是基于可编程超大规模集成电路和计算机技术发展起来的一门重要技术,DSP芯片的快速数据采集与处理功能以及片上集成的各种功能模块为DSP应用于各种场合提供了极大的方便。而CMOS图像传感器与CCD相比,由于CMOS图像传感器能将时序处理电路和图像信号的前端放大与数字化部分集成 于一个芯片内,因而其发展一直受到业界的高度重视。现在,随着技术与工艺的发展,CMOS图像传感器不仅在噪声上得到了有效改善,而且分辨率也得到了明显提高。CMOS图像传感器将以其低廉的价格、实用的图像质量、高集成度和相对较少的功耗在视频采集领域得到广泛的应用。为此,本文提出了一种基于DSP和CMOS图像传感器,同时由复杂可编程逻辑控制芯片CPLD控制的实时图像采集系统的实现方案。

1 硬件设计

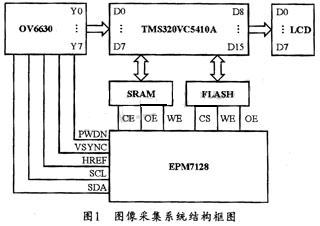

图1所示是该图像采集系统的电路结构框图。由图1可见,该图像采集系统主要由OV6630图像传感芯片、CPLD控制模块、SRAM数据存储器、FLASH程序存储器、DSP信号处理器等几部分组成。其图像采集芯片用美国Omni Vision公司开发的彩色CMOS图像传感器OV6630,该芯片与传统的CCD传感器相比,其最明显的优势是集成度高,功耗小,生产成本低,容易与其它芯片整合。该芯片将CMOS光感应核与外围支持电路集成在一起。由于其运用了专有的传感器技术,因而能够消除普通的光电干扰。该芯片的像素阵列为352×288,即101376像素,还有4行、4列可供选择。图像数据的输出有多种格式(YCrCb4:2:2,GRB4:2:2和RGB原始数据输出格式),本系统选用8通道Y输出RGB原始数据输出格式,以及逐行扫描的工作方式。其输出格式为:

奇数扫描行BGBG……

偶数扫描行GRGR……

根据人眼对彩色响应带宽不高的大面积着色特点,每个象素没有必要同时输出3种颜色。因此,数据采样时,奇数扫描行的第1,2,3,4,…象素分别采样和输出B,G,B,G,…数据;偶数扫描行的第1,2,3,4,…象素分别采样和输出G,R,G,R,…数据。在实际处理时,每个象素的R,G,B信号由象素本身输出的某一种颜色信号和相邻象素输出的其他颜色信号构成。这种采样方式在基本不降低图像质量的同时,可以将采样频率降低60%以上。

系统中的核心处理芯片选用TI公司的加强型定点DSP芯片TMS320VC5410A,该DSP的工作频率可达160 MHz,内部有64KBRAM空间可以灵活的映射为数据或程序存储空间。由于DSP的内部存储空间有限,所以,本设计在外部扩展了一大小为1 MB的SRAM数据存储器CY7C1021和256 K的FLASH程序存储器SST39VF400A。控制芯片CPLD选用Altera公司的MAX7000系列芯片EPM7128SLC84-15。该芯片包含84个I/O管脚、128个宏单元,每16个宏单元可组成一个逻辑阵列块,工作电压为5.0 V。该芯片在系统中处于总体时序控制地位,既用于给图像传感器芯片提供控制信号。也用于SRAM和FLASH的片选和读写控制,同时还负责LCD的显示控制。

2 软件设计

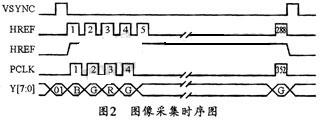

当系统配置完毕以后,便可以进行图像数据的采集与处理。在采集图像的过程中,最主要的工作是判别一帧图像数据的开始和结束的时刻。在仔细研究了OV6630输出的同步信号(VSYNC是垂直同步信号、HREF是水平同步信号、PCLK是输出数据同步信号)的基础上。笔者用VHDL语言实现了采集过程起始点的精确控制。图2所示为图像采集期间三个同步信号与数据信号的时序关系图。

图2中,每一个帧同步信号VSYNC周期包含288个水平同步信号HREF脉冲,而每一个HREF周期包含352个PCLK时钟脉冲,每一个PCLK时钟可输出一个RGB像素的视频数据。

传感器相关文章:传感器工作原理

评论