基于VIM的嵌入式存储控制器的研究与实现

1 引言

本文引用地址:http://www.amcfsurvey.com/article/265390.htm随着VLSI技术的迅猛发展,微处理器主频日益提高、性能飞速增长,尽管与此同时存储器集成度也越来越高、存取延时也在不断下降,但是处理器性能的年增长速度为50%~60%,而存储器性能每年提高的幅度只有5%~7%,DRAM存储器的低带宽和高延迟使高性能处理器无法充分发挥其性能,处理器和存储器之间速度的差距越来越成为制约整个系统性能的瓶颈。众多的研究者从微体系结构出发,采取乱序执行、多线程、预取、分支预测、推断执行等技术,或多级Cache的层次式存储结构来弥补微处理器与存储器性能差距,但是这些技术存在多种问题:复杂、占用面积大、资源利用率低、造价高、耗尽存储带宽等,并不能真正解决存储瓶颈问题。即使一些新的存储器产品的出现,如DDR存储器,Rambus存储器等,虽然一定程度上提高了存储器的频率,但处理器和存储器之间的性能差距还是在进一步拉大。如何才能真正消除存储器性能瓶颈呢?PIM技术(Processing in Memory),即把处理器和存储器紧密集成到一块芯片上,半导体制造工艺的进步使CMOS逻辑单元可以和SRAM或DRAM集成在一个硅片上,这样可以突破芯片间引脚的限制,充分发挥存储器的隐藏带宽,同时降低访问延时(将片间访问延时转换成片内访问延时迟)。以PIM技术为基础,用向量部件作为协处理器构成的Vector In Memory(VIM)体系结构,可充分发挥PIM高带宽、低延迟、低功耗的特点,开发数据级并行,是解决存储系统性能瓶颈的有效途径。本文具体阐述VIM体系结构中影响存储系统性能的关键部件嵌入式存储控制器的设计与实现。

2 VIM体系结构

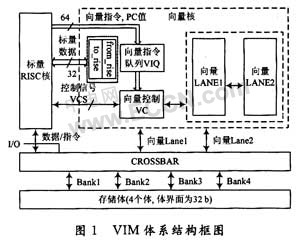

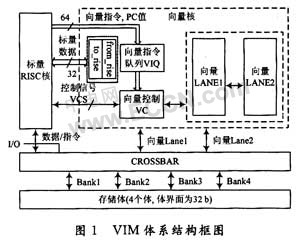

VIM是一种面向流式数据处理的向量体系结构,其微体系结构的处理器部分由1个标量核和1个向量协处理器构成,嵌入式存储控制器和存储器构成片上DRAM存储系统,处理器部分和存储系统之间由高速存储交叉开关互连。VIM体系结构最重要的特征就是向量处理器和嵌入式存储器的结合。图1中给出了VIM系统结构的典型框架结构。

2.1 RISC标量核

VIM标量核为可综合、高集成度的32位RISC处理核,其指令集与SPARC V8兼容;标量核包括整数部件、浮点部件,支持用户态和超级用户态(管态)2种工作模式;主要功能是执行标量指令(SPARC指令集),处理异常和中断,为向量部件输送向量指令,完成标量核与向量部件之间的数据传递,并与主机进行通信完成取指、译码工作。

2.2 向量部件

向量部件作为标量核的协处理器,执行扩展的向量指令,与标量部件并行执行。由向量指令队列、向量控制器、向量核寄存器文件、向量Lane等部分构成。向量指令队列VIQ,为异步FIFO队列。标量核通过部分译码将识别出的向量指令写入VIQ,由向量取指单元从中顺序取出指令交由译码部分再次译码。向量控制器保证向量指令的正确执行,完成向量流水线控制。向量核寄存器文件由向量寄存器文件、标量寄存器文件、控制寄存器文件和标志寄存器文件构成,包括32个32位寄存器。向量Lane由并行的向量流水线构成,包括完全流水的LSU,ALU,FPU等部件。每个Lane可以看成一条数据通路,完成对特定宽度数据的处理,多个Lane之间可以并行执行。

2.3 嵌入式存储系统及I/O

嵌入式存储系统由存储互连交叉开关、嵌人式存储控制器和存储器构成,存储互连交叉开关用于片内运算部件访存时的地址翻译、访存指令的路由以及读取数据的返回,其将标量访存部件、向量Lane访存部件和嵌入式存储器互连起来,具有多端口、高带宽、低延时的特点。嵌入式存储控制器接收从存储交叉开关传送过来的访存指令,实现对DRAM的数据存取。存储器是由4个独立的存储体组成的一个多体交叉存储器,每个存储体都有自己独立的存取控制接口,体内又分成4个子体。采用多体存储器可使映射到不同存储体的访存指令可以同时执行,并行对多个向量元素进行操作,同时每个存储体都对应各自的存储控制器,相对于集中式存储控制而言访问延时更低、功耗更小。I/O接口用于实现多个VIM节点间互连和挂接一些I/O设备。

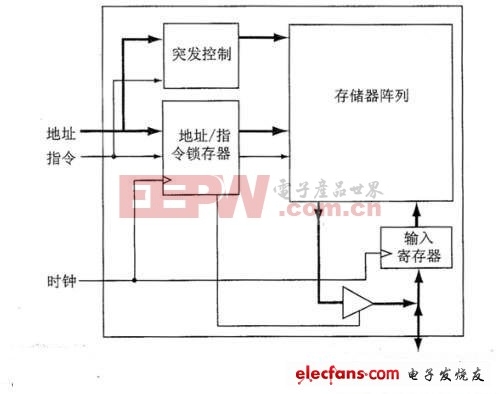

嵌入式存储控制器实现对DRAM存储体的初始化、激活、行选、列选、自动充电、定时刷新、读延迟、写恢复等功能控制,支持4种突发读写模式、两种行选延时选择,具有严格的时序。下面将详细阐述嵌入式存储控制器的设计方案,设计思想以及具体实现。

3 嵌入式存储控制器设计与实现

3.1 嵌入式存储控制器模块结构

存储控制器是系统总线和DRAM之间的控制接口,在VIM的存储系统中,嵌入式存储控制器的作用就是将存储交叉开关所传输过来的读写控制命令转换成DRAM的控制信号实现对DRAM的读写、刷新等控制;将存储交叉开关传输过来的地址分解成Bank地址、行地址和列地址,在特定的时候传输到DRAM地址线上;以及控制数据总线和DRAM数据线的数据输入输出。

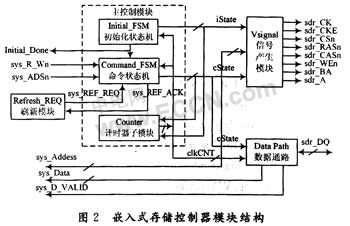

实现VIM-1嵌入式存储控制器,图2所示为其模块结构,存储控制器由主控制模块、信号产生模块、刷新模块和数据通路构成。

下面具体对每个模块的功能进行阐述:

存储器相关文章:存储器原理

评论