基于FPGA的m序列信号发生器设计

m序列是一种伪随机序列(PN码),广泛用于数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域。基于FPGA与Verilog硬件描述语言设计井实现了一种数据率按步进可调、低数据误码率、反馈多项式为

本文引用地址:http://www.amcfsurvey.com/article/263588.htm

的m序列信号发生器。系统时钟为20MHz,m序列信号发生器输出的数据率为20~100 kbps,通过2个按键实现20 kbps步进可调与系统复位,输出误码率小于1%.

m序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种伪随机序列。是由移位寄存器、反馈抽头及模2加法器组成。m序列一旦反馈多项式及移位寄存器初值给定,则就是可以预先确定并且可以重复实现的序列,该特点使得m序列在数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域使用广泛。因此,深入学习研究m序列具有重要的实际意义。

1 m序列信号发生器的组成

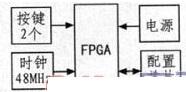

基于FPGA的m序列信号发生器硬件结构极其简单,仅需两个独立按键(一个是复位按键与另一个控制数据率切换按键)、一个48 MHz的用于提供系统时钟有源晶振、系统电源、一块配置芯片、几个简单的电阻与电容即可实现。按键去抖动、按键复位、按键切换数据率、时钟分频等功能均在FPGA内部编程实现。

图1 信号发生器硬件组成框图

2 m序列信号发生器的关键设计

本文中m序列信号发生器的反馈多项式为

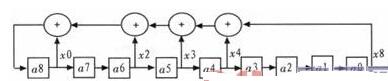

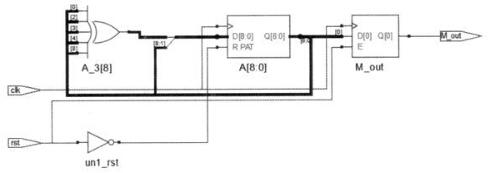

其反馈及移位寄存器的关系图如图2所示。

图2 m序列信号发生器反馈及移位寄存器图

从本设计中的反馈及移位寄存器的关系图可以看出,一个时钟周期,移位寄存器右移一位,最高位输入为x0、x2、x3、x4及x8的异或(模2相加)。m序列的输出是移位寄存器的最低位。图2所示的关系是m序列呈现为随机性、周期性的根本原因。

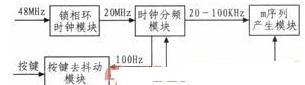

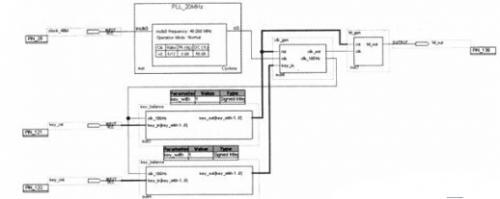

为了满足信号发生器输出数据率20 kbps的步进通过按键可调,则生成按步进20 kbps可调的时钟是实现该功能的关键。当按键发生,时钟的输出频率加20 kbps.在实际电路中,按键会有很大抖动,对系统会造成很大的不稳定性,因此,必须想办法减小这样的不利影响。在FPGA中一般使用硬件描述语言,描述一个延时电路,来实现按键去抖动的目的。该设计中信号发生器的FPGA内部各功能模块及其之间的关系,如图3所示。

图3 FPGA功能模块方案框图

3设计核心之综合与仿真

3.1时钟模块设计

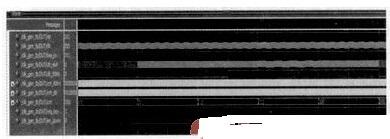

在所有基于FPGA的设计中,设计满足设计要求的时钟信号对设计成败起着至关重要的作用。满足在本文所设计的m序列信号发生器的时钟信号输出频率为:20 MHz、20 kHz、40 kHz、60 kHz、80 kHz、100 kHz.输出的时钟信号在modelsim 6.5f中的仿真波形如图4所示。从图4中可以看出,时钟模块性能满足设计要求,设计正确。

图4 时钟产生模块仿真波形

3.2 m序列产生模块设计

m序列产生模块是m序列信号发生器的最核心部分。文中的m序列生气器核心模块的verilog的代码为:

从Verilog代码可以看出,m序列产生模块实现极其容易,只需要一个移位寄存器、一个模2加法器即可实现m序列的产生。

图5 m序列产生模块Symplify综合效果图

图6 m序列信号发生器系统仿真波形图

本系统中m序列产生模块在Synplify综合结果图、在modelsim 6.5f中的仿真波形图,分别如图5、6所示。从图5、6中可看出,该模块产生了周期为217的周期序列,设计正确。图7是系统的quartus II顶层模块图。

图7 系统顶层模块图

4结论

当信号发生器的移位寄存器A的初值A=9‘b1_0000_0000时,m序列的周期T=217,输出的周期m序列为:0000000011111010110011011111000110100110101110110000011011011001001110011001111111011110000101010011110110100010100001100101111010010010100101101010101111110011101110000001011100100011000011101010001110001001000010001.

该信号发生器实现了输出数据率在20~100 kbps之间,并实现按20 kbps的步进可调功能;输出数据率仅在输出60 kbps的数据率时有较大误差,数据率偏小约0.2%.该m序列信号发生器性能稳定,实现所有设计功能,符合设计要求。

fpga相关文章:fpga是什么

负离子发生器相关文章:负离子发生器原理 晶振相关文章:晶振原理 离子色谱仪相关文章:离子色谱仪原理

评论