为何Zynq SoC平台可以使企业的产品利润激增(二)

平台:实现盈利衍生品的最佳战略

本文引用地址:http://www.amcfsurvey.com/article/263142.htm面对不断增加的研发成本、日渐激烈的竞争以及消费者对更好产品日益苛刻的需求,越来越多的半导体公司和电子产品系统公司开始转向寻求平台战略来快速创建衍生产品并最大限度提高盈利性。平台战略能够进一步降低产品开发时间、加速上市进程并节省工程时间成本,同时能够提高各种衍生产品或新一代产品的盈利性。

正如IBS研究所显示,企业通过开发衍生设计“优化收入和利润”。而采用平台方法在相同节点开发多种衍生产品(也就是说,衍生产品的衍生产品)使企业能够进一步优化收入与利润,因为各个后续设计都能受益于在之前设计中学到的经验教训、重新利用以及对客户需求更准确的了解。

处理选择是平台成功的关键

企业在实施平台战略时做出的两项最重要的业务决策实际上是关键技术决策:众多处理系统中哪一个会成为产品平台的核心?该处理系统的哪种芯片实施方案最适合提高盈利性?

在平台战略中,处理系统必须满足或者超过应用软件和系统需求。它必须具备可扩展性并且易于扩展;必须具有不断增长的大型成熟生态系统;而且必须允许设计人员和工程师利用之前的设计成果。最后,它必须来自具有发展规划且成熟稳定的供应商,而且该供应商并未持有偏离其发展规划或者不断推出无尽勘误的不良记录。虽然有一些候选产品符合上述某些要求,但是能够满足或超过全部上述要求的系统是ARM微处理器架构。

|

|

生命周期收入* (百万美元) |

研发支出(百万美元) |

生命周期净利润** (百万美元) |

净现值*** (百万美元) |

盈利能力指数 |

|

初始复杂ASIC |

$1300 |

$130 |

$260 |

$12.85 |

0.1 |

|

1号衍生品 (80%市场规模) |

$1040 |

$35 |

$208 |

$74.78 |

2.14 |

|

2号衍生品(80%市场规模) |

$650 |

$35 |

$130 |

$34.47 |

0.98 |

* 假设7年。

** 假设利润率为20%。

*** 假设贴现率为15%。

表1 – 开发衍生设计具有可观的净现值(NPV)和更加出色的盈利性指数。

ARM已经成为PC之外一切设备的事实标准嵌入式架构。如今采用高级嵌入式处理技术的绝大部分电子系统——从手机、汽车到医疗设备——都采用ARM处理器内核。尤其是ARM的Cortex-A9处理器架构成为许多种片上系统(SoC)的核心。其不仅已用于专门针对前言智能手机、平板电脑等高量产增值产品开发的ASIC设计中,而且还用于众多ASSP设计,该设计主要针对那些希望进军由于缺乏功能差异化而主要展开价格竞争的中小规模成熟市场的公司而开发。

为了增强产品差异化,许多企业基于ARM处理系统创建了将FPGA与现成ASSP融为一体的产品平台。他们可以在这种配置中实现硬件与软件细分,从而创造更广泛的特性组合或者灵活、可升级、性能更高的终端产品——其可帮助他们战胜那些提供仿效式仅可软件编程的ASSP实施方案的竞争对手。在这些ASSP中添加赛灵思FPGA已经帮助众多企业的产品在市场中脱颖而出。

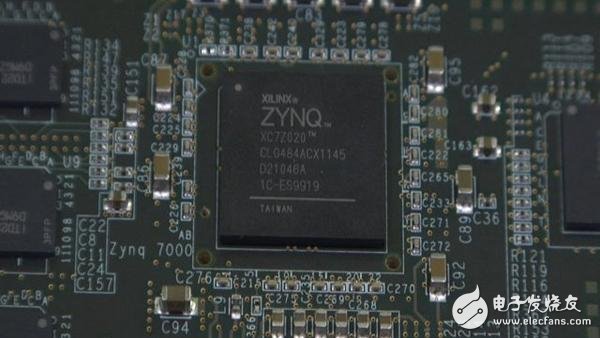

理想平台解决方案:ZYNQ SoC

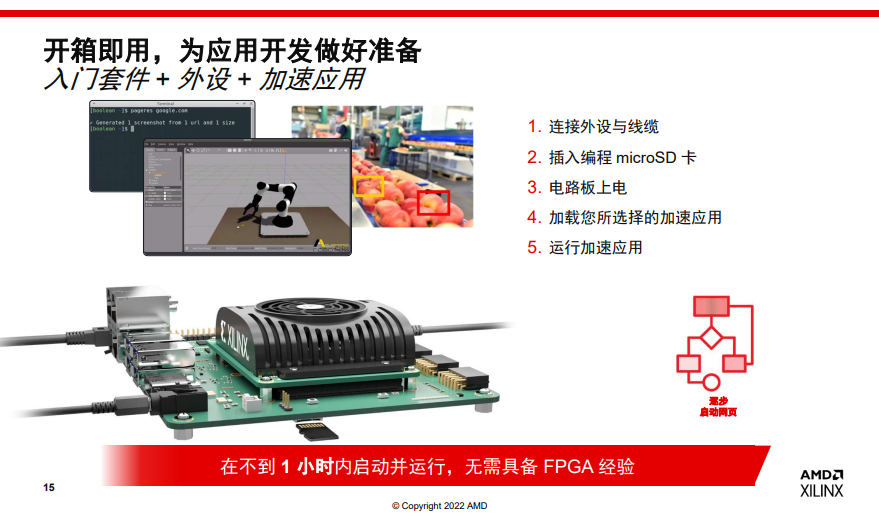

借助Zynq-7000 All Programmable SoC,赛灵思正在实施适合绝大部分嵌入式应用的高稳健性ARM Cortex- A9平台解决方案。如表2所示,作为一种芯片平台,Zynq SoC具备超过ASIC、ASSP以及ASSP+FPGA组合的众多优势。与ARM处理系统的其他硬件实施方案相比,Zynq SoC不仅在NRE、灵活性、差异化、生产力/上市进程等方面具有最佳特性组合,而且还具有最低衍生品成本和最低整体风险(表3)。

另外,Zynq-SoC与其他平台实施方案相比具有巨大的成本优势。让我们来看一下具体数据。

赛灵思 All Programmable SoC产品营销与管理总监Barrie Mullins表示,设计28nmASIC的平均成本是1.3亿美元,而ASIC设计项目的10倍收入目标则为13亿美元。他指出,但是,基于Zynq SoC的典型设计项目本质上其整体设计成本比ASIC实施方案低得多而且上市进程也比其快。其原因是Zynq SoC能够提供预设计、特征化、业经测试与验证的成品SoC,其可以带来软件、硬件、I/O性能以及差异化灵活性。此外,Zynq SoC还受益于低成本且高度集成的赛灵思硬件与软件设计工具,而ASIC工具流程不但复杂,而且具有严重的互操作性及兼容性问题,同时还需要支付高达数百万的许可费用。设计人员采用赛灵思推荐的UltraFast™方法时赛灵思的设计流程会尤为优化。Mullins补充到,由于赛灵思生态系统IP已经完成设计和预验证并且赛灵思工具可以生成中间件,因此IP认证成本较低。

|

|

系统总成本 |

灵活性 |

差异化 |

上市进程 |

衍生品成本 |

风险 |

|

Zynq SoC |

低+最高价值 |

最灵活:硬件与软件可编程性 + 可编程I/O |

可编程性最高,硬件/软件协同设计 |

集成硬件与软件差异化速度最快 |

硬件与软件可编程性带来最低成本 |

可预测的低风险 |

|

ASSP + FPGA |

高于Zynq SoC (与系统相关) |

非常灵活,但是与Zynq SoC相比ASSP I/O有局限性 |

硬件与软件可编程性取决于ASSP |

如果ASSP需要硬件细分,则速度最快 |

中低成本,取决于FPGA厂商 |

中低风险,取决于FPGA厂商 |

|

ASSP |

如果只需纯软件可编程性,则最低 |

良好灵活性,但是仅具备软件可编程性 |

仅具备软件可编程性 – 便于克隆 |

如果仅需纯软件细分,则速度最快 |

如果需要纯软件衍生品,则成本最低 |

如果仅需纯软件可编程性,则有可能风险最低 |

|

ASIC |

极高,以致无法承担。 |

制成后仅具备有限软件灵活性 |

最佳硬件细分,但是软件细分有局限性 |

速度最低且风险最高 |

最高 |

极高(重新设计) |

最佳平台特性

良好平台特性

一般平台特性

最差平台特性

表2 – Zynq-7000 All Programmable SoC可为寻求实施平台战略的客户提供理想的特性组合。

|

最低NRE与最佳风险降低 |

最高灵活性与差异化 |

更高生产力与更快上市进程 |

最低衍生品成本与最高盈利性 |

|

√ 成品芯片 √ 开发与设计工具成本微不足道 √ 赛灵思IP库 + 第三方IP √ 广泛的开发板 |

√ All Programmable 硬件、软件与I/O √ 具备随时现场可编程性 √ 部分重新配置 √ 安全的系统(加密) |

√ 即时硬件/软件协同开发 √ All Programmable 抽象(C、C++、OpenCV、OpenCL、HDL、基于模型的输入) √ Vivado Design Suite、Vivado HLS、IP Integrator 与 UltraFast方法 √ 广泛、开放的OS与IDE支持(开源Linux及Android、FreeRTOS、Windows Embedded、Wind River、Green Hills等) |

√ 基于ARM AMBA AXI4实现IP标准化 √ 重新利用预验证代码(ISO、FCC等) √ 重新利用和优化代码与测试文件 √ 量产芯片、电源电路、PCB与IP许可授权。 |

表3 – 低NRE费用、灵活性等要素使Zynq SoC成为平台战略的理想选择。

Mullins指出,因此典型Zynq SoC项目需要2300万美元。由此实现设计项目的标准10倍收入目标需要生命周期收入达到2.3亿美元——此10倍目标比实现ASIC实施方案所需达到的13亿美元10倍目标更易于实现,而且也更可行(表4)。

采用的上述方法分析IBS数据时,如果我们假设在Zynq SoC 中实现的初始复杂设计能够完全占领同样的13亿美元目标市场,则利用57名工程师只需要2300万美元就能够在两年内完成产品。

如果假设初始Zynq SoC设计具有与初始ASIC设计相同的20%利润率,则初始Zynq SoC设计的NPV为1.0727亿美元,而PI为3.7,其明显优于初始ASIC的1285万美元NPV和仅有0.1的PI。利润率同样为20%的Zynq SoC的NPV与PI更加可观(表5)。

|

|

28nmASIC(IBS数据) |

|

Zyng SoC (赛灵思估算) |

|||

|

% |

大概工程月数 |

总成本(百万美元) |

% |

大概工程月数 |

总成本(百万美元) |

|

|

硬件 |

|

|

|

|

|

|

|

IP认证 |

26 |

704 |

11.8 |

20 |

240 |

4.0 |

|

架构 |

8 |

209 |

4.2 |

45 |

100 |

2.1 |

|

验证 |

53 |

1431 |

28.9 |

35 |

160 |

3.0 |

|

物理设计 |

13 |

350 |

6.9 |

0 |

0 |

0 |

|

硬件小计(设计工程资源) |

100 |

2694 |

51.8 |

100 |

500 |

9.1 |

|

软件 |

|

4296 |

59.8 |

|

720 |

10.0 |

|

原型成本(百万美元) |

2.1 |

1.0 |

||||

|

原型验证 |

|

815 |

16.6 |

|

140 |

2.8 |

|

总计 |

|

7805 |

130.3 |

|

1360 |

22.9 |

c++相关文章:c++教程

评论