矽穿孔技术襄助 3D IC提高成本效益

应用直通矽晶穿孔(TSV)技术的三维积体电路(3DIC)为半导体业界提供全新境界的效率、功耗、效能及体积优势。然而,若要让3DIC成为主流,还必须执行许多基础的工作。电子设计自动化(EDA)业者提供周延的解决方案支援3DIC革命,包括类比与数位设计实现、封装与印刷电路板(PCB)设计工具。半导体厂可以运用这个解决方案,满足高效率设计应用TSV技术的3DIC的所有需求。

本文引用地址:http://www.amcfsurvey.com/article/262452.htm随着更高密度、更大频宽与更低功耗的需求日益增加,许多IC团队都在期待应用TSV技术的3DIC。3DIC以更小的体积容纳丰富的功能,实现「超越摩尔定律(MorethanMoore)」的完善整合,以及更高的效能与更低的成本。3DIC封装可以容纳许多异质晶粒,如逻辑、记忆体、类比、射频(RF)与微机电系统(MEMS)于不同的制程,例如28奈米(nm)的高速逻辑与130nm的类比。这样可以为系统单晶片(SoC)整合提供替代方案,延迟投入新制程时的昂贵转移动作,让开发人员能够在单一封装中容纳更多的功能。

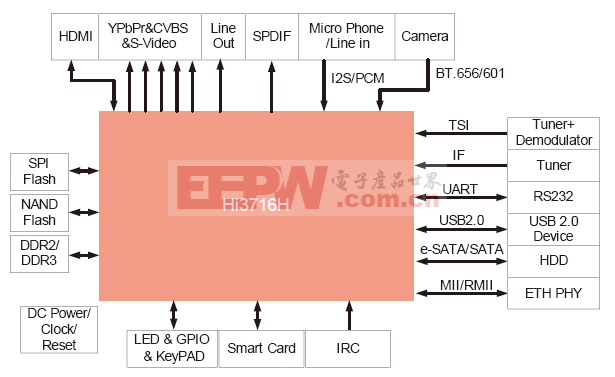

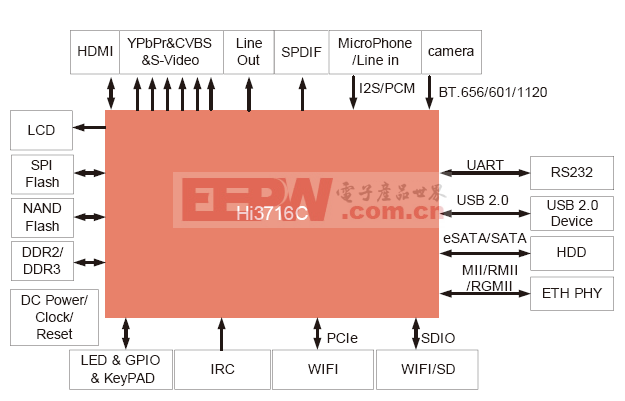

应用TSV技术的3DIC预料将对网路架构、绘图、行动通讯与运算等领域造成广泛的冲击,尤其是对需要超轻、小巧、低功耗装置的应用影响更钜。具体的应用领域包括多核心中央处理器(CPU)、绘图处理器(GPU)、封包缓冲器(PacketBuffer)/路由器、智慧手机、平板电脑、迷你电脑(Netbook)、相机、DVD播放机和电视机上盒。

尽管大家兴趣盎然,但这项技术仍在萌芽阶段。缺乏标准定义,供应链生态系仍然捉摸不定,还有设计、验证和测试挑战仍须解决。本文说明3DIC技术的概要,并讨论设计挑战、生态系统要求及所需解决方案。尽管多年来市面上一直有许多多重晶粒封装流通着,本文聚焦于运用TSV技术堆叠晶粒的晶片设计实现(SiliconRealization),尤其是堆叠不同类型晶粒的应用,如逻辑、记忆体、类比、数位或RF。

从设计的观点而言,好消息是3DIC不需要大规模更新工具(Retooling),不需要新的「3D」设计系统,制程技术方面也没有明显的跃进。但是,结构分析、平面规画、绕线与布局、发热分析、时序、讯号完整性、IC/封装协同设计与测试等领域需要新的功能。有些新功能现在已有,还有些则仍待开发。

对3DIC而言,晶片实现是不可或缺的方法。晶片实现有许多形式,包括类比与数位矽智财(IP)区块、整个IC与系统晶片,或者3DIC。无论最终产品如何,晶片实现流程有三个特点:一致的设计与验证意图、适当运用更高阶抽象化,以及聚合实体、电子与制造资料成为圆满的「签核(Signoff)」流程。成功的3DIC设计环境可在第一时间掌握设计意图、运用早期判断与平面规画来支援抽象化,甚至透过测试、设计实现、萃取、分析与封装工具而达成聚合。

TSV3DIC优点多

现今,SoC在单一晶粒中纳入令人难以置信的大量功能。SoC通常包含处理器、数位逻辑、记忆体与类比元件,搭配嵌入式软体。有些SoC拥有数亿闸道,速度推升至千兆赫(Gigahertz)等级。

然而,传统单晶粒SoC有一些缺点。其一就是,所有元件都采同一制程并放置在同一晶粒上,而类比与RF设计在先进制程的挑战性极高。如果设计团队尝试在先进制程建置类比电路,可能需要花费许多时间开发和测试必要的IP区块,还要应付变异性与漏电等与制程相关的问题。

单晶粒SoC的其他挑战还有混合讯号整合与验证。类比与数位电路布局太过于接近时,会导致许多问题;或者,敏感的类比或烦人的数位元件可放置在独立的IC上,但是那就必须在不同封装之间传递讯号,导致耗电且会降低效能。

或许当今SoC设计的最大问题就在于日渐高涨的开发成本。依据业界估计,SoC软硬体开发在32nm制程可能高达1亿美元。此外,冗长的开发循环会导致额外成本。如果成本无法降低,先进制程SoC唯有在少数量大的应用下,才具有可行性。

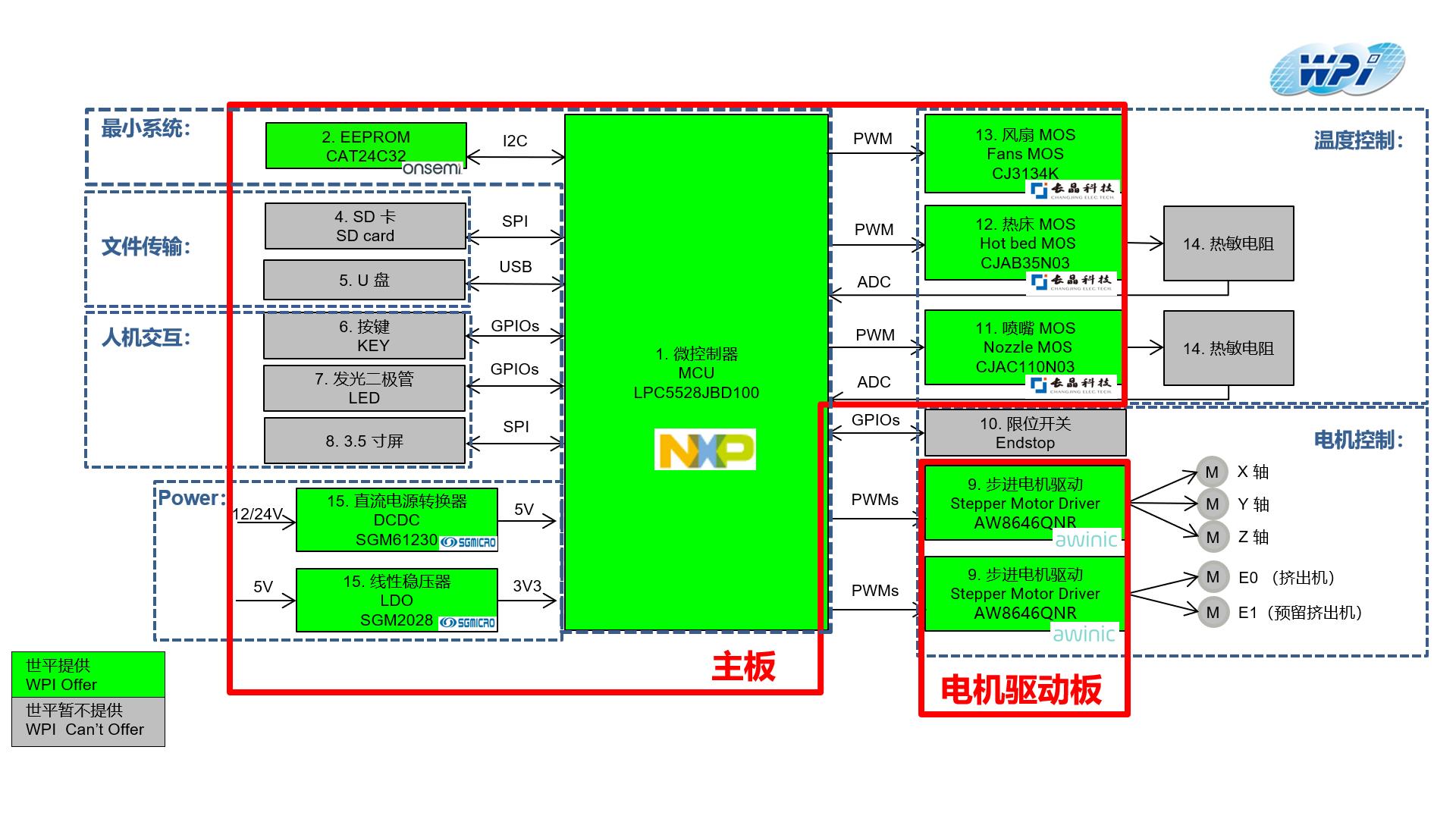

单晶粒SoC还有一个替代方案,就是将众多晶粒放置到单一封装中,例如可使用90nm制程于类比/RF电路,而28nm制程于数位逻辑(图1)。多重晶粒封装技术有系统级封装(SiP)、晶片封装(Silicon-in-package)和多重晶片模组(MCM)等不同说法,就是将众多晶粒放置到用来连结彼此的共同基板上。这些技术于1990年代初期开始普及。

图1SoC与SiP的比较

SiP做法提供一些胜过SoC设计实现的优势,包括可以运用各领域最适当的技术制程来建置类比、数位和记忆体等各种晶粒。除逻辑、记忆体、类比和RF功能之外,现代化SiP也包括天线或镜子等微机电系统(MEMS)元件。

多年来进化的其他封装选项还有封装体内嵌(PiP),将许多更小的SiP放置在较大的SiP中,以及封装层叠(PoP)将一个SiP放置在另一个SiP之上。PiP与PoP都可归类为3DIC,但是在效能、功耗、密度与体积优势却都不如应用TSV技术之3DIC。

直到最近,已经可以运用打线接合(WireBond)与/或覆晶(Flip-chip)技术,将矽晶粒附加到SiP基底上。现在,可以增加矽中介层基底(SiliconInterposerSubstrate)(被动或主动),提供更佳的晶粒间(Die-to-die)互连,提高效能也降低功耗。矽中介层也包括TSV,提供从上金属层到附加的背面金属层的连线(图2)。有时,这种技术也称为2.5D堆叠(2.5DStacking)。

图2运用TSV技术新增矽中介层(仅显示两颗晶粒以简化说明)

TSV就是贯穿矽晶粒的垂直电子连结,TSV是直径范围1?30微米的铜通道。运用TSV技术的「真正」3DIC,包含两个以上运用TSV技术连接在一起的晶粒,例如运用传统覆晶技术将一颗包含TSV的晶粒附加到SiP基底上。同时,第二颗晶粒黏贴到第一颗晶粒上(图3)。

图3运用TSV技术的简单3DIC架构图

图3所示3DIC可称为背面对正面(B2F)构态,因为第一颗晶粒的背面黏贴到第二颗晶粒的背面。也可以是背面对背面(B2B)与正面对正面(F2F)构态,尤其是堆叠两颗以上的晶粒。

撰写本文时,两层以上晶粒彼此堆叠的情况还很常见,而较大晶粒垫底,黏上两颗以上较小晶粒的状况就不常见了。未来,

我们预期,一定会看到越来越多图4所示的状况。

图4更复杂的3DIC加入六颗晶粒

与传统Soc相比,运用TSV技术的3DIC的优势可汇整如下:

.成本可以更低,因为类比与记忆体等所有功能都不必转移到先进制程。

.更容易满足高速互连与频宽的需求,就先进记忆体技术而言,可达到每秒100Gbits。

.3DIC可以微型化,节省电路板空间也缩小产品体积,最适合于极端轻巧的行动装置。

.3DIC可降低功耗,因为不需要庞大的驱动器。3D堆叠可使用更低功耗的小型输入输出(I/O)驱动器。甚至,更低的电阻/电感/电容(RLC)有助于降低功耗。

.封装之间的互连减少,可以实现更快的效能与更低的功耗。

.上市前置时间更短;这归功于模组化、「晶粒重复利用」的可能性,以及能够将类比/RF丢给更高制程处理。

.光子学(Photonics)或MEMS等新兴技术可能整合到3D堆叠中。

与打线接合SiP相比,TSV提供更低的RLC寄生、更高效能、更省电且更密集的设计实现。与矽中介层作法相比,垂直式3D晶粒堆叠提供更高水准的整合、更小的体积和更快速的设计循环。但是3D堆叠也造成一些额外的挑战,包括散热、时脉与电源管理问题。下面将详细讨论这些挑战。

3DIC设计仰赖多方合作

尽管运用TSV技术的3DIC并不需要革命性的崭新3D设计系统,却必须在既有工具增添一些新功能,以便数位设计、类比/客制设计和IC/封装协同设计。这些功能应支援三大矽晶实现目标:一致的设计意图、抽象化与聚合。终极目标就是要以最短的周转时间,实现系统成本最佳化。如果3DIC不具有成本与时间效益,就不可能普及。

首先,需要周延的解决方案。许多3D堆叠将结合数位与类比/RF电路,需要强大的类比/混合讯号功能,因为堆叠晶粒的独一无二封装需求,必须要有IC/封装协同设计功能。此外,将3DIC定位在电路板上也是一大挑战,需要功能强大的PCB布局系统和适当的分析工具。换言之,任何所谓的完美「解决方案」都必须提供数位、类比、IC、封装与PCB设计方面的专业能力。

3DIC设计有赖众志成城。封装设计人员知道要在哪里放置脚位,但是不明瞭IC的设计。IC设计人员能够将TSV放入晶粒中,却不了解封装。PCB设计人员必须将3DIC封装和其他元件一起整合到电路板上。3DIC需要以往各自为政的所有团队密切合作与协同设计。

TSV有一些特殊的工具需求。主动层中的TSV必须由IC设计工具来设计,但主动层中的TSV必须以封装或SiP工具来规画。被动层中的TSV必须用封装或SiP工具来规画和设计。矽中介层最好是用数位IC设计工具来设计。

强化生态系统3DIC标准至关重要

标准将成为3DIC生态系统的重要环节。刚开始的标准活动可能会聚焦于定义术语的分类,接着是记忆体、逻辑与中介层等介面之间的I/O标准化。

同时,3DIC联盟正聚焦于制造面,并发表记忆体互连标准(IMIS),以应标准化垂直互连的需求,还有另一个标准化领域就是3DIC测试。两项新兴的标准--IEEE1149.7compactJTAG与IEEEP1687internalJTAG(iJTAG)可以部署在一起,成为3DIC中的嵌入测试架构。

适用于嵌入核心测试的IEEE1500标准让IP核心脚位得以受控制和观察。同样的原则可能也适用于存取3D堆叠中的个别晶粒。IEEE1500「核心测试包」的观念环绕核心而部署离散傅立叶转换(DFT)封包。在3DIC中,这种观念会将整颗晶粒打包起来,且可透过生产级I/O介面来存取。同样的测试模式也可在封装测试层重复利用。

应用TSV技术的3DIC代表半导体业界的重要新趋势,在许多应用领域都提供令人注目的耗电量、效能与体积优势,且能够遏止不断攀高的SoC开发成本。因为开发人员能够堆叠来自不同制程的晶粒,就不再需要将类比与RF等所有系统元件移动到单一制程。

尽管从设计或制程观点而言没有重大改变,3DIC要迈进主流使用者的量产作业,还有许多仍待努力之处,如需要系统层探勘、3D平面规画、设计实现、萃取/分析、测试以及IC/封装协同设计等领域的新功能。为实现最佳、即时、高成本效益的设计,3DIC晶片实现流程应支援一致设计意图、抽象化及实体与制造资料的聚合,必须要有定义妥善的生态系,包括晶圆厂、IP供应商、电子设计自动化(EDA)供应商与半导体委外封测(OSAT),还有设计套件与参考流程。

高成本效益的3DIC设计需要三大领域的协同设计:晶片、封装与电路板,方能使应用TSV技术的3DIC达到高成本效益目标。

路由器相关文章:路由器工作原理

路由器相关文章:路由器工作原理

漏电开关相关文章:漏电开关原理

评论