基于现场可编程门阵列(FPGA)技术的射频读卡器设计

与其他常用的自动识别技术如条形码和磁条一样,无线射频识别(RFID)技术也是一种自动识别技术。每一个目标对象在射频读卡器中对应唯一的电子识别码(UID),或者“电子标签”。标签附着在物体上标识目标对象,如纸箱、货盘或包装箱等。射频读卡器(应答器)从电子标签上读取识别码。

基本的RFID系统由三部分组成:天线或线圈、带RFID解码器的收发器和RFID电子标签(每个标签具有唯一的电子识别码)。表1显示了常用的四个RFID频率及其潜在的应用领域。其中,目前商业上应用最广的是超高频(UHF),它在供应链管理中有可能得到广泛的应用。

EPC电子标签

EPC表示电子产品代码,是RFID电子标签的标准,它包括电子标签的数据内容和无线通信协议。EPC标准将条形码规范中的数据信息标准与ANSI或其他标准化组织(802.11b)制定的无线数据通信标准结合在一起。目前应用在供应链管理中的EPC标准,属于第二代EPC Class-1标准。

|

Class-1标签在出厂时已经被写入,但也是可以现场下载。通常情况下,一旦标签已被写入,内存即被锁定不可再次写入信息。Class-1标签采用常规的分组传输协议—读卡器发送包含相关命令和数据的数据包,标签随后做出响应。

恶劣的读卡器应用环境

RFID的应用环境可能非常恶劣。信道的工作频率是免许可的工业、科技与医药(ISM)频带。此频带中的RFID读卡器受到来自无绳电话、无线耳麦、无线数据网络以及其他临近读卡器的干扰。必须将每一读卡器的RF接收器前端设计为能够抵御强干扰信号,避免产生可导致询问错误的失真。接收器的噪声必须保持在较低的水平,以便具备足够的动态范围,从而以无错方式检测出低电平标签响应信号。

|

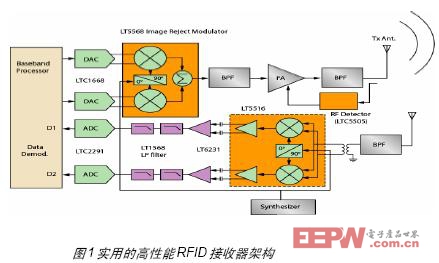

实用和可靠的射频接收器设计

接收器的核心是Linear公司的LT5516,这是一种高度集成化的直接转换正交解调器,芯片上提供了一个精确正交移相器(0度至90度)。来自天线的信号在通过射频滤波器之后,通过一个不平衡变压器直接输入到解调器输入端口。由于LT5516的噪声系数很低,在不需要低噪放大器(LNA)的情况下,仍能保持其21.5dBm IIP3和9.7dB P1dB的性能。

在接收数据时,读卡器发射连续载波(未调制),以便为标签提供电源。在收到请求后,电子标签通过对载波进行调幅,响应一个码流。所采用的调制方式为幅移键控(ASK)或者反相-幅移键控键控(PR-ASK)。解调器带有两个正交移相检出式输出端口,因此具备天然的分集接收功能。如果由于多路或相位取消导致某个通道无法接收信号,另一条通道(移相90度)就可接收较强的信号,反之亦然。这样,整体接收可靠性就得以提高。

一旦解调完成,即可将I(相内)和Q(正交相位)差分输出信号以AC方式耦合至一个运算放大器(被配置为一个差分放大器),随后被转换为单端输出信号。这个时候应将高通角频率设置为5KHz,低于接收数据流的最小信号频率,高于最大多普勒频率(可能被运动标签采用),同时保持高于电力线频率(60Hz)。这样,输出信号就能利用被配置为四阶低通的LT1568顺利穿过低通滤波器。低通角频率应被设置为5MHz,以便最大码流信号穿过滤波器,达到基带。

基带信号然后被一个双路低功耗模数转换器(LTC2291,分辨率为12位)进行数字化处理。由于标签码流的带宽为5KHz至5MHz,LTC2291能够以25MSps的速率进行充分的采样,从而精确地捕获解调信号。在需要的时候,还可在基带DSP中实现额外的数字滤波。这样,接收器就能具备最大的逻辑阈值设置灵活性,该设置可由基带处理器以数字化方式执行。本文引用地址:http://www.amcfsurvey.com/article/261476.htm

基带任务和数字化射频信道化处理,可提高用全FPGA解决方案实现的吸引力和集成度

高动态范围射频发射器设计

发射器集成了一个镜像抑制直接转换式调制器。LT5568具备很高的线性度和较低的背景噪声,因此能够为所发射的信号提供出色的动态范围性能。调制器能够从数模转换器(DAC)接收正交式基带I和Q信号,然后直接调制至900MHz发射频率。

在内部,LO(本地振荡器)被精确正交移相器分割。经调制的射频信号被合并为一个单端、单边带射频输出信号(镜像被抑制了46dBc)。此外,调制器还带有匹配的I和Q混合器,从而最大限度地抑制了LO载波信号(至-43dBm)。

复合调制电路具备出色的邻道功率比(ACPR),有助于满足发射频率屏蔽要求。例如,当调制器射频输出电平为-8dBm时,ACPR指标优于-60dBc。由于具备更出色的ACPR性能,信号可被放大至许可的1w功率(在美国为+30dBm),或者放大至2w,以符合欧盟规范。在上述两种情况下,重要的是保持电平固定,因为该电平用于向电子标签提供电源,并最大化读卡距离。LTC5505型射频功率检测器的内部温度补偿功能,可准确地测定功率,提供稳定的反馈信号,以调节射频功率放大器的输出功率。

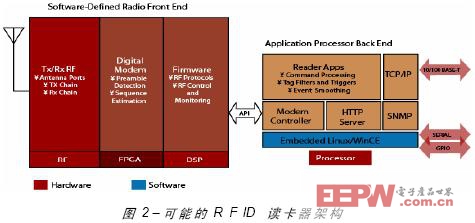

基带处理和网络接口

在基带频率上,FPGA执行发送至DAC和来自模数转换器(ADC)的波形的信道化任务。这一过程也被称为数字中频

处理,涉及滤波、增益控制、频率转换和采样率变化等。FPGA甚至可以并行处理多个信道。

|

- 先导字段检测

- 排序估计

- 调制和解调(ASK、频移键控和相移键控)

- 信号产生

- 相关器处理

- 峰值检测和阈值设定

- CRC纠错和校验和

- 编码和解码(NRZ、Manchester、单极性、差分双极性和Miller)

- 帧检测

- ID去扰

- 安全加密引擎

所收到的RFID标签数据可通过串口或网络接口被传送至企业系统服务器。这种传统的架构正逐步演变为一个高级分布式 TCP/IP 网络的一个部分。在该网络中,射频读卡器将负责管理临近的标签。

在这种情况下,射频读卡器就象是电子标签和连接至企业软件系统的智化分布式数据库之间的网关。

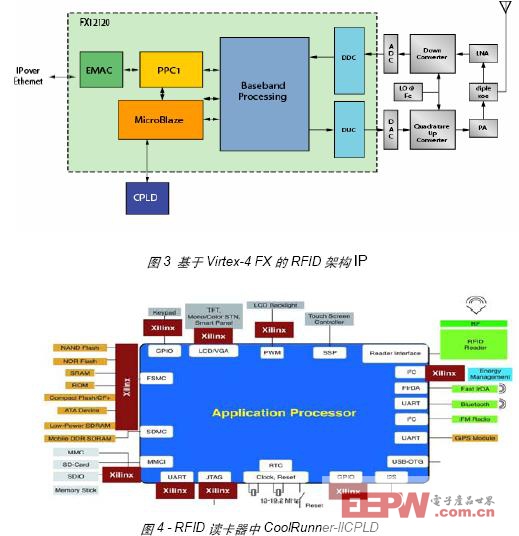

取决于硬件/软件功能分区情况,这些基带任务即可在FPGA上完成,也可在DSP上完成,或者由二者联手执行。Xilinx公司推出了一个IP内核套件,其中包括FIR、CIC、DDS、DUC、DDC、比特相关器、正弦/余弦LUT等。这些逻辑电路非常适合执行加密引擎任务(加密引擎采用移位寄存器和XOR)。针对Xilinx® VirtexTM-4系列的DSP48引擎十分适合执行其他信号处理任务。

一个基带处理器负责控制各种基带处理任务的功能性和调度,还负责链路层协议。这些基带处理任务包括跳频、发送前侦听、防冲突算法处理等。基带处理器还提供了以太网、USB、固件等接口。

基带任务和数字化射频信道化处理,可提高全FPGA解决方案的吸引力和集成度。FGPA功能、DSP功能,以及基带处理功能,都可被整合于一个带有嵌入式处理器的FPGA。

|

PowerPC/MicroBlaze嵌入式处理器执行以下任务:

- EPC数据处理和前转

- 协议处理

- 询问调度

- TCP/IP 网络接口

- 控制和监视

- 调制解调器控制

- 升级代理

- HTTP服务器

- SNMP/MIB处理

Xilinx千兆以太网系 统 参 考 设 计(GSRD)是一个基于EDK的参考系统,能够在基于TCP/IP的协议接口和用户数据接口之间搭起一座高性能的桥梁。GSRD的组件具备满足TCP/IP系统每比特和每包开销要求的功能。

Xilinx还针对Monta Vista Linux 和 Treck堆栈提供了发射性能基准。采用 Xilinx Platform Studio (XPS)微处理器库定义的Nucleus PLUS RTOS,为采用MicroBlaze和PowerPC处理器的系统带来了新的优势。Nucleus PLUS RTOS尺寸很小,这意味着它能够利用片上现有的存储器,从而最大限度降低功耗,提高性能。此外,广泛的中间件使得Nucleus PLUS RTOS成为RFID后端网络的理想选择。

利用XilinxCoolRunnerTM-II型CPLD,手持式射频读卡器可连接至硬盘驱动器、QWERTY键盘、可移动硬盘接口、各种显示设备和其他计算机外设(如图4所示)。这些CPLD还能帮助应用处理器,并且满足低功耗、高性能和更小芯片封装等要求。

结论

将来,射频读卡器很可能具备前端 DSP功能,比如射频协议处理等。如今,这些功能在独立式DSP中进行处理,将来,它们很有可能被集成于FPGA。嵌入式软处理内核已可显著提升DMIPS/MHz性能,不久以后,高版本的处理内核将取代控制读卡器应用程序的后端外部处理器,从而借助可编程逻辑最大限度地提高射频读卡器设备的灵活性,同时最大限度降低其成本。

Xilinx 决 心 不 断 改 进 其XtremeDSPTM 和MicroBlaze可配置软处理内核,从而不断增强FPGA的DSP及嵌入式处理功能。

作者:Niladri Roy Xilinx公司垂直市场营销部ISM分部高级经理

Akshaya Trivedi Xilinx公司垂直市场营销部无线分部高级系统工程师

James Wong Linear公司产品行销经理

评论