微带滤波器与耦合器电路的设计,制作与测量

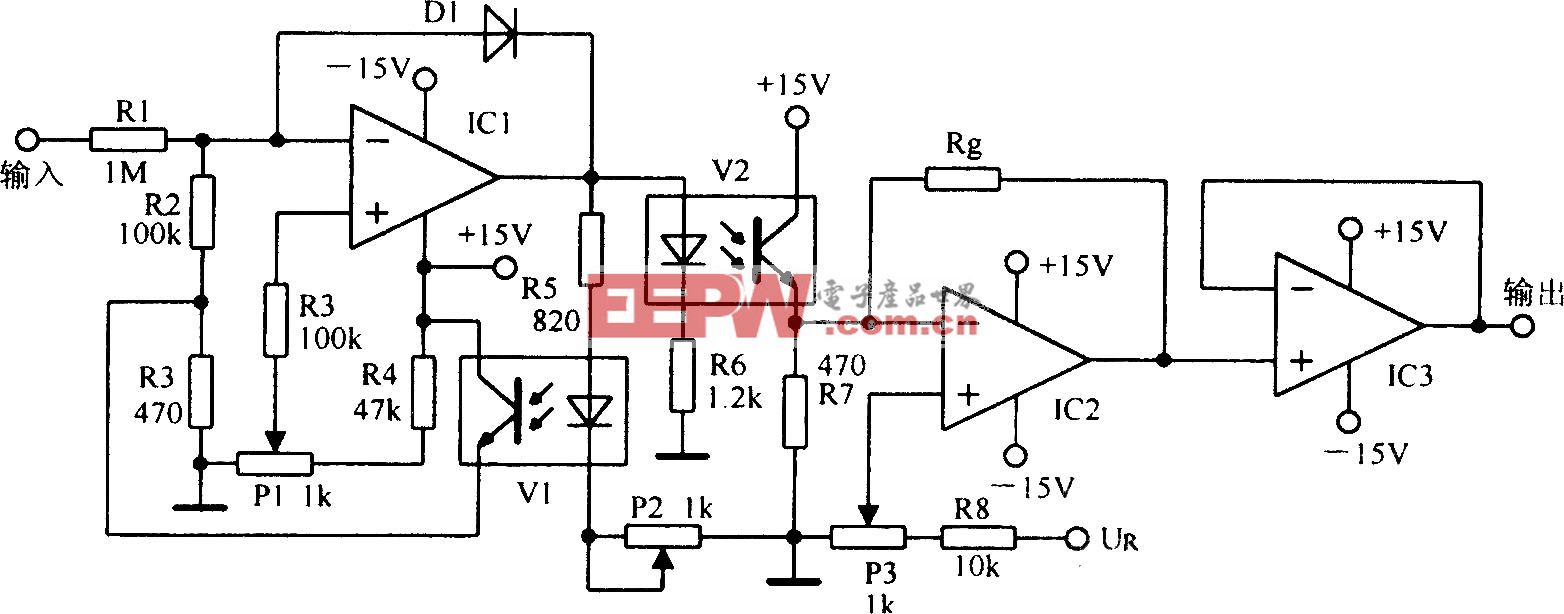

今日的微波设计者使用多种工具以帮助自己实现有效的电路和系统设计。他们借助的资源包括他们的参考书库,功能强大的EDA软件,电磁(EM)分析工具,以及 他们的个人经验。通常,他们的设计需要通过制作最终的电路板成品,并对其进行测试来得到验证。我们用不同的设计方法设计了两种微带电路,并且利用电路板雕 刻机快速制作了样品;根据两个样品的测试结果的比较来判断这两种设计方法的优劣。

本文引用地址:http://www.amcfsurvey.com/article/259749.htm

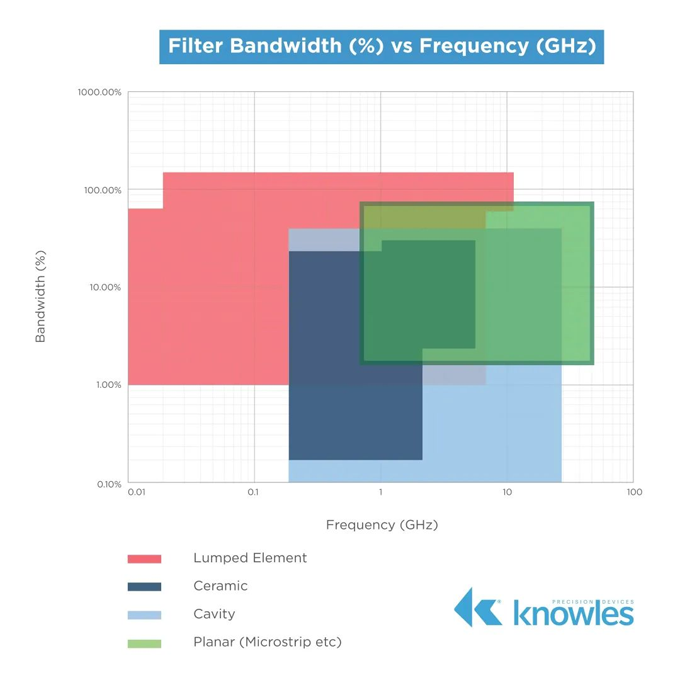

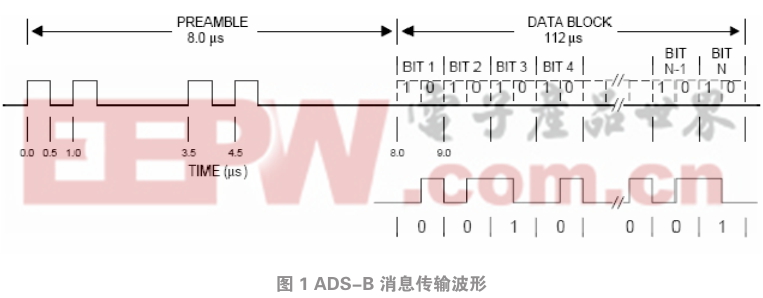

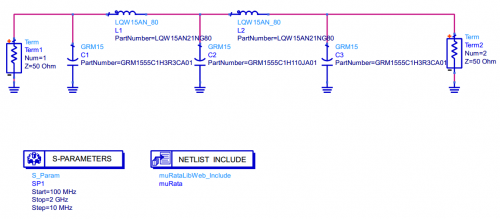

要求设计的样品是经典的发夹式滤波器,带宽要求在3.7 到4.2GHz;还有一个1到8GHz单向耦合器,我们使用了Schiffman锯齿技术来减小它的尺寸。发夹式滤波器使用Agilent公司的 ADS1.3[1]来做设计和模拟,而平面电磁分析则利用Sonnet Lite [2]完成。与此不同,耦合器的设计从已有的阶梯线耦合器开始,采用了设计规则变换的方法来完成。以上的两个电路都使用了LPKF激光电子的 ProtoMat C100HF电路板雕刻机完成制作。结果使用HP (Agilent) 8753E网络分析仪做了测量。

设计实例 #1:一个3.7GHz到4.2GHz的发夹式滤波器

这个滤波器要求在3.7GHz到4.2GHz波段内平直响应,并且插损和回损要求控制在16dB以内。我们选择了经典的发夹式设计,因为经验告诉我们,它能够达到所要求的性能和尺寸。

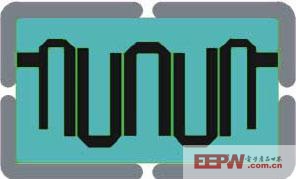

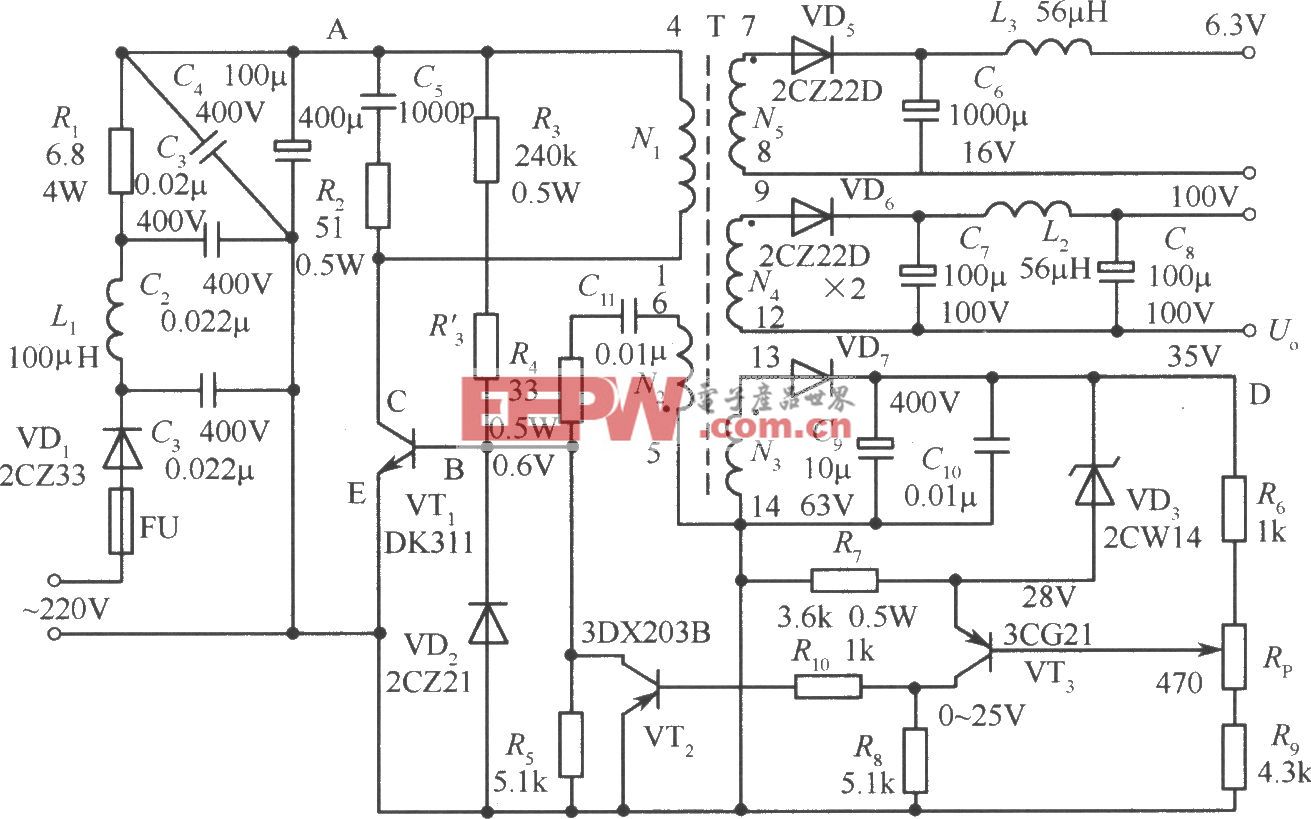

这个滤波器使用ADS1.3设计,设计图见图1。这个当然就是我们所熟悉的发夹式设计。滤波器所占据的面积大约是0.5*1.2 英寸,另外还要加上发夹电路外足够大的面积来保持介电特性的一致性。

图2是ADS中的设计和优化设置。由于这个拓扑结构是中心对称,它被设计成两部分背靠背的形式。如此一来,对称的设计让之后的模拟计算变的简单,计算的时间大幅减小。

优化所设定的目标是以最少16dB的回损实现3.55到4.4GHz范围内的带通滤波,3.2GHz以下,4.7GHz以上28dB stopband attenuation。优化的频率区间是3.0到5.0GHz。更大的范围没有必要。

图3是ADS给出的每个滤波器的最终设计图,包括了端口,微带线,T字,转角以及stubs。注意到stub末端的0.1pF的电容end effect(散射电容)。这些在图1中也有。

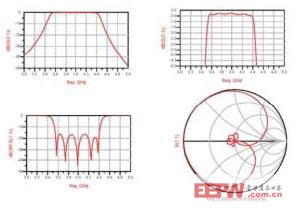

该模型的性能由图4给出。这些图显示了ADS模拟的带通,截止,回损的结果以及输入输出阻抗比的Smith图。这些图显示,ADS的设计模型能够满足滤波器相应的设计标准。

EM分析

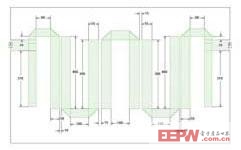

图5是表示滤波器的所有尺寸。这份设计图被Sonnet Lite平面电磁场分析软件用来做电路性能分析。

图6是EM分析的结果。这里的带通波段比ADS预言的略窄,但是已经包含了3.7到4.2GHz波段。通带平整度与ADS给出的结果非常接近。通带内的回损响应没有ADS给出那么对称,但是在整个范围内保持在16dB 左右。

图6 Sonnet Lite的EM分析结果。从结果可以看出相关响应满足设计标准。

制作测试滤波器

为了比较发夹滤波器的设计模型和实际效果,我们在微波覆铜板上使用雕刻机制作了一个测试样品。

ADS的设计图样,经过简单处理之后,变成雕刻机的驱动文件。设计图中的相应尺寸被直接调用到LPKF的配套软件中。图7是LPKF CircuitCAM产生的加工数据。

性能测试

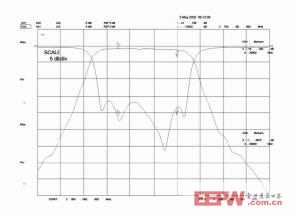

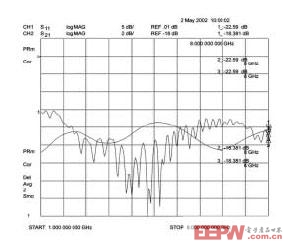

板子被铣成设计图样后,我们两端接上连接器,并且用HP 8753E网络分析仪对滤波器进行了测量。图8是样品滤波器的透过性能 (S21) 以及回损 (S11)测量值。这个图的比例是每格5dB,用以说明整体通带/截止性能小于-45dB。

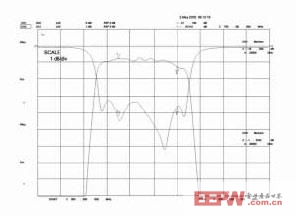

图9与图8相同,不过带通的比例为每格1dB,用以说明通带的平整度。图中回损依然是每格5dB。

实测结果与模拟结果符合的很好。通带比ADS预言的稍窄,但比Sonnet Lite给的值小。三种建模方法和测量结果在插入损耗和通带平整度方面都符合得很好。

尽管从回损的形状上讲,模型和实测结果都各不相同,但是每一个都达到了16dB的规格要求,而且清晰显示出多极滤波器特有的驼峰响应。

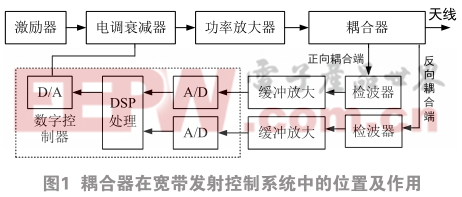

设计实例 #2:一个缩小了的阶梯线单向耦合器

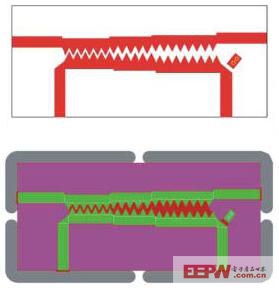

下一个我们将要检查的电路是用经验技术开发的。我们想要考察一种减小微带电路尺寸的Schiffman方法, Uysal[4]在他的文章中详细论述了这种方法。这一技术使用锯齿或之字结构来减少给定电路的机械长度。

一 个由CAP Wireless职员Paul Daughen-baugh使用ADS设计的1到8GHz阶梯线耦合器被作为设计底稿。设计的最终结果被导出到CircuitCAM软件,经过简单处理之 后,输出成雕刻机能够识别的设计图样,见图10。这张图清晰展示了这一技术。

我们采用了一种经验的方法来从直条的耦合器得到锯齿状的耦合器,具体规则如下:

- 闭合空间耦合器部分——要求之字线的总长与这部分的直线长度相等。这就使得这个部分的尺寸缩小了将近一半。直线之间的间距保持不变。

- 开放空间耦合器部分——这个第三部分的线间距由锯齿的中心高度为准计算的。在这个开放空间,我们假设场将根据这个平均空间来耦合,而不是沿着第一部分的边缘线。同时,在这一部分长度的将小将相对较少。作为简化,我们采用了与最初直线部分相同的长度。

- 中心部分——中心部分线间距和长度较小是根据第一和第三部分的几何平均值计算而得的。

这个“最佳猜想”方法是必要的,因为不可能使用现有的软件对这个结构进行分析。甚至对Sonnet Lite而言,都已经过于复杂。

耦合器性能

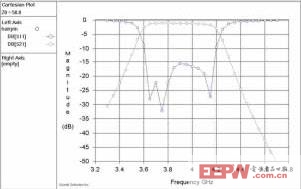

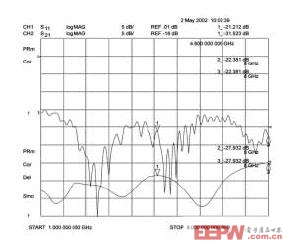

耦合器利用LPKF雕刻机制作完成后,我们在1到8GHz间对耦合度进行了评估。在图11中,耦合端口传输是那条相对平滑的线。图中的中心水平线为 -18dB,每格表示2dB。在整个测量频率范围内,耦合值为–19 dB ±1.5 dB。在同一副图中,输入回损为每格5dB,从上往下数,第二条线表示0dB基准线。最坏情况的回损在最低频率处,为16dB。

图 12表示逆向耦合的情况,包括了输出端口回损。两个图的分辨率都是每格5dB。对于逆向耦合,中心线依然是-18dB基准线,耦合值在整个波段中好于 -28dB,除了高频端处处好于31dB。输出端口回损的比例与图11中的相同,同时也在1GHz时有最差的16dB响应。

除了超高频区域,方向性(前向耦合减去逆向耦合)总体保持在10dB。设计目标是大于10dB,实际设定目标为12dB,以便保留足够的富余。对大多数的波段,目标都已经达成,我们认为,对初次尝试而言,这已经是非常不错的结果了。

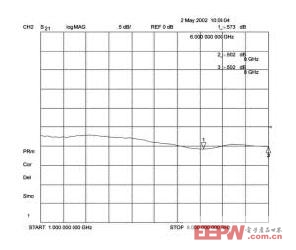

图13是插入损耗,它在1GHz时,为0.25dB;在6GHz时,有一个0.57dB的最坏结果。从1到8GHz范围内,插入损耗的变化不超过0.33dB。

样品板铣制机的使用

快速制作样品电路板能够彻底改变某些设计的工程实现方法。以单向耦合器为例,我们一开始准备做多次反复的设计以获得需要的性能。带着几分运气(还有经验基础上的猜想),第一次尝试就获得了一个好的耦合器。

图14和15展示了铣制得到的电路板,在上面已经安装了连接器以供测量之用。图14展示的发夹式滤波器电路甚至显示出一小块经过焊接的电路,这是为了填补微带线路的一个缺口。这是由于设计图样上有一个很小的差错,在板子完成时,才被发现。

耦合器设计可能还需要修改以便改进低端回损或者让响应更平坦。这些细小的改动可能不会被使用传统电路板制作方法的公司考虑。随着环境规则的变化,特别在加州,额外的环境费用和复杂的工艺流程使得大多数的公司不再保留室内蚀刻实验室。

总结

我们希望通过这些实例能够清楚展示我们是如何使用诸多设计资源的。为了设计和制作这些滤波器和耦合器电路,几个工程师的经验再加上参考书,先进电路理论模拟,电磁分析还有制作和测量才能完成。过程中的每一步都会影响最终的设计的成败。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

评论