微带滤波器和耦合电路的设计

1 前 言

当今的微波设计师依靠很多工具来制作高效的电路和系统。他们要利用已有的参考资料和强大的EDA工具和电磁(EM)分析工具,还必须结合自己的实践经验来 进行制作。这些工作终极需要通过制作电路和测试完成的电路来实现。这篇文章描述了两个微带电路设计是如何使用各种不同工具开发,用电路板铣制设备快速制 作,然后经过丈量来验证设计方法的正确性。

样例中的设计是一个典型的带宽3.7到4.2GHz的发夹型滤波器和一个1到8GHz的定向耦合器,使用Schiffman锯齿技术减小尺寸。发夹型滤波器用Agilent ADS1.3软件设计和仿真,用SONnet Lite软件进行平面EM分析。耦合器运用了基于设计规则的变换,有一个现存的门路线形式的耦合器设计来启动。

两个电路都是用LPKF光电股份有限公司的Protomat C100HF型设备制作出来的,使用HP(Agilent) 8753E网络分析仪获得丈量结果。

2 设计样例

3.7到4.2GHz的发夹型滤波器

2.1 设计

这个滤波器设计用于在3.7到4.2GHz的带宽上获得一个平坦的响应。插进损耗和回波损耗在此频段优于16dB。这个滤波器用在下变频器输进端进行镜频抑制。该设计选用一个典型的发夹型滤波器,它将能满足设计要求的性能和尺寸。

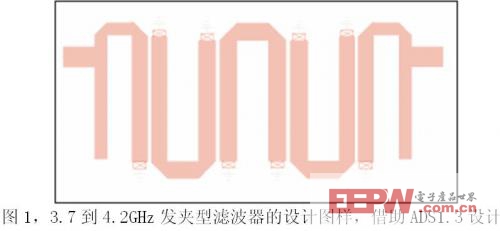

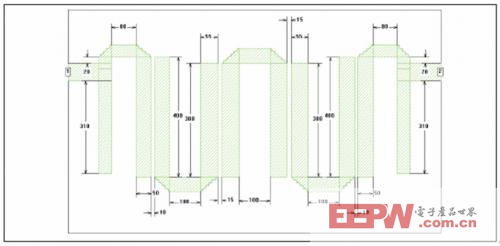

滤波器由ADS1.3设计,图1是结果图样。当然,这是一个熟悉的发夹型结构。滤波器占用的面积约为500 x 1200 mils (0.5 x 1.2 in.),包括用来保持恒定逻辑属性的发夹循环所需的足够面积。

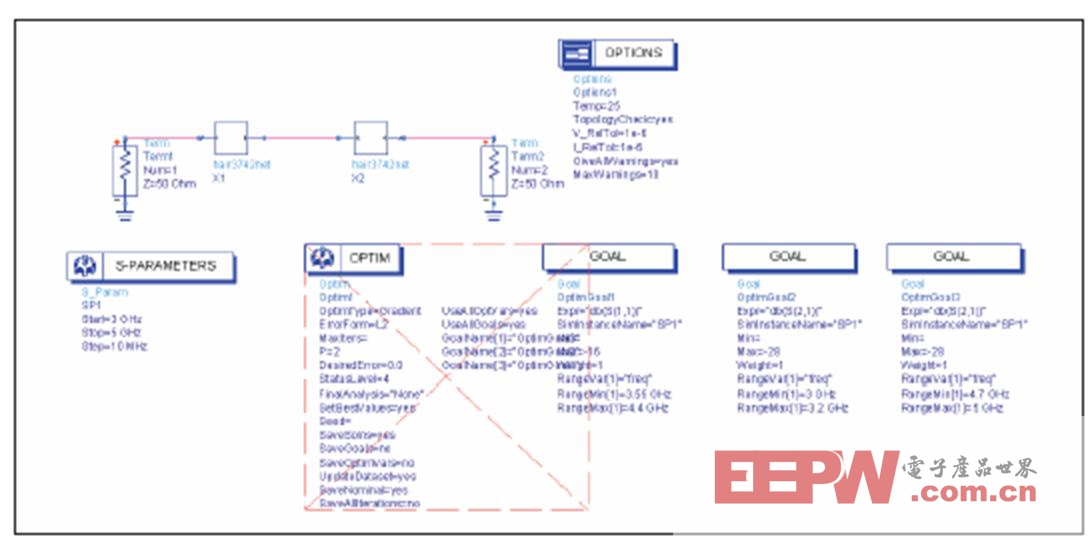

图2是在ADS中的设计和优化结构。这个拓扑形是中心对称的,所以设计成两段,由一个“背靠背”结构连接。由于数学方面上的结构尺寸减小,计算时间被大大缩减。

图2,在ADS中的设计和优化结构。滤波器以两个镜像的图形块进行仿真,以实现对称结构

建立优化来获得在通带3.55至4.4GHz的最小16dB的回波损耗,在3.2GHz以下和4.7GHz以上最小28dB的阻带衰减。优化的频率范围是3.0-5.0GHz。更宽范围不要求获得预想的结果。

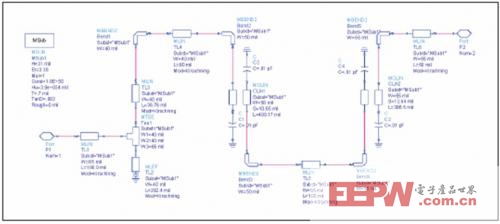

图3,对终极设计的ADS仿真定义。仿真性能和滤波器图样都出自于这里的数据

图3显示了每一个“半滤波器”的ADS终极设计,包括端口、微带线、T形、弯曲和短凸形。留意短凸形的末真个0.1pF电容,说明具有末端效应(边沿电容)。图1的也有它们的显示。

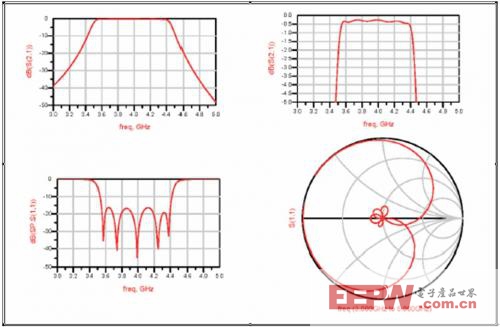

图4,仿真结果。

(a)全程响应;(b)通带响应和插进损耗;(c)回波损耗;(d)Smith阻抗图

图4是模型化的性能显示。包括通带、阻带特性、回波损耗结果以及输进/输出阻抗的Smith图。这些图表说明ADS模型满足滤波器的设计标准。

2.2 EM分析

图5是滤波器尺寸的详图。设计的数据使用Sonnet软件公司的Sonnet Lite平面电磁场软件进行电路分析。

图5,滤波器的具体尺寸。

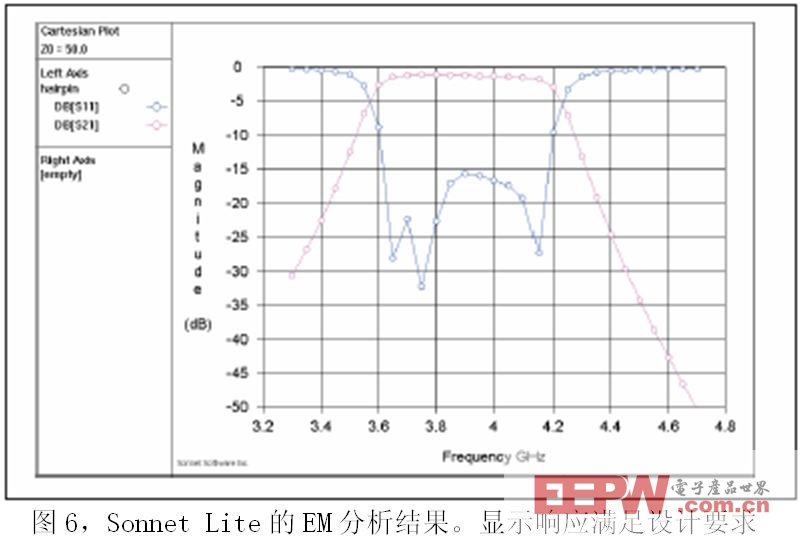

图6是EM分析结果。通带的响应比ADS预期的稍稍窄一些,但是假如制作出来的电路性能满足分析的话,仍将覆盖3.7到4.2GHz的带宽。通带的平坦性 非常接近ADS模型。回波损耗的响应在通带上比ADS仿真的对称性稍差一些。但仍能保持16dB或更好。

评论