小型化LTCC低通滤波器设计与制造工艺研究

1 引言

本文引用地址:http://www.amcfsurvey.com/article/259665.htm低温共烧陶瓷技术(LTCC)技术是20世纪80年代中期发展起来的一种新型电子工艺技术,最初用于航空航天工业和大型计算机中高密度多层陶瓷基板电路的加工与制造,随着现代通信技术的发展,各类通信设备和终端对小型化的要求越来越高。

LTCC技术能够充分利用三维空间,在基板内埋植电容、电感、天线、滤波器、功分器等无源器件,集成度高,尺寸小,射频性能优良,利用LTCC这种可以多层结构埋植器件技术,可以很好地满足设备小型化的要求。

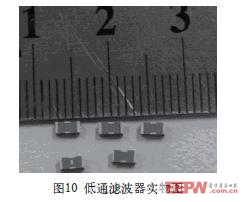

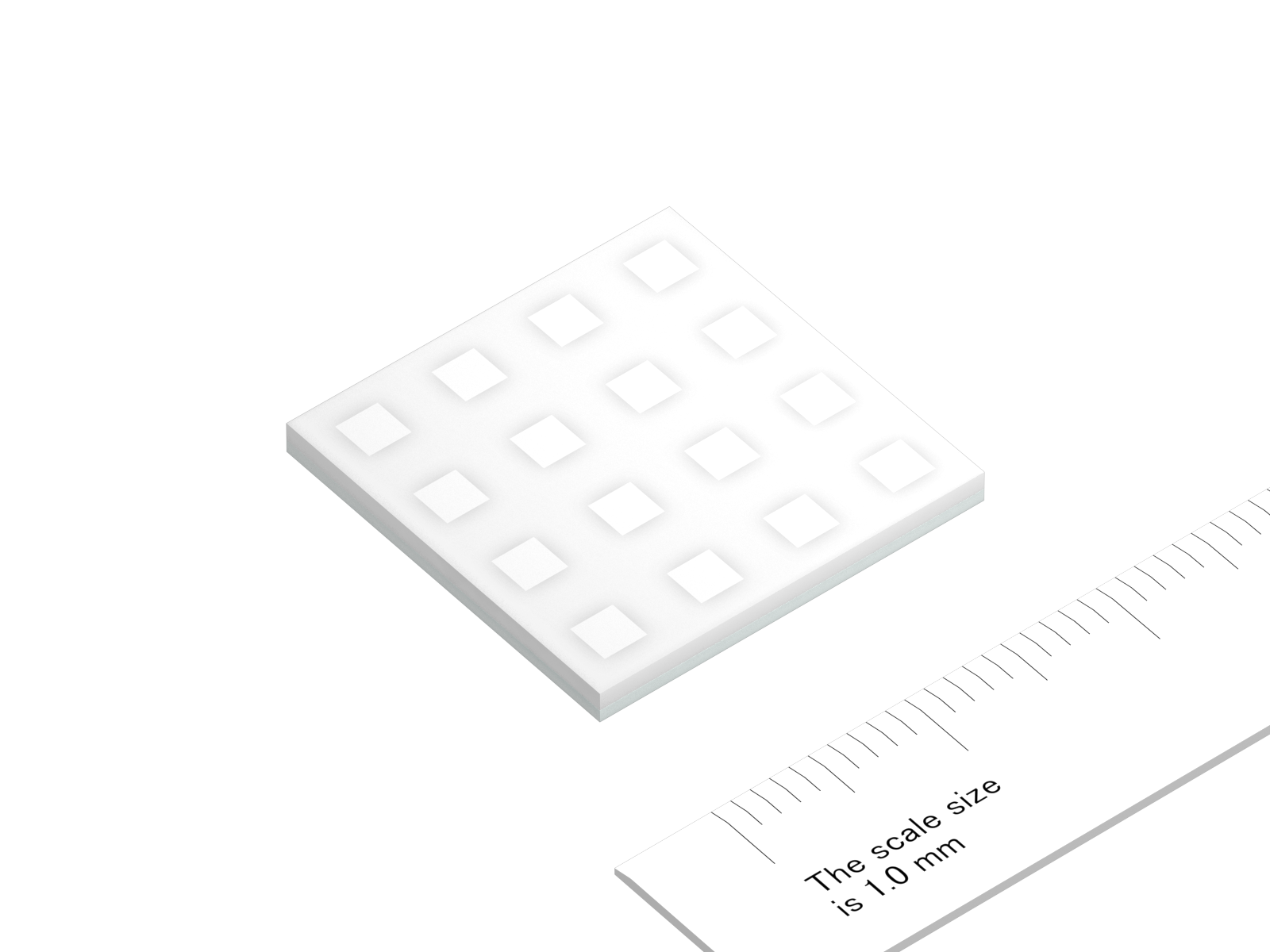

LTCC一个重要应用就是制作各种小型化滤波器等无源器件,目前,商用LTCC低通滤波器的典型尺寸主要有1812(4.5 mm×3.2 mm)、1210(3.2 mm×2.5 mm)、1206(3.2 mm×1.6 mm)等规格。本文中提出的滤波器利用LTCC多层布线三维立体结构的特点,大大减小了器件的面积尺寸,平面尺寸只有3.2 mm×1.6 mm,达到了小型化的目的。

2 LTCC低通滤波器的设计

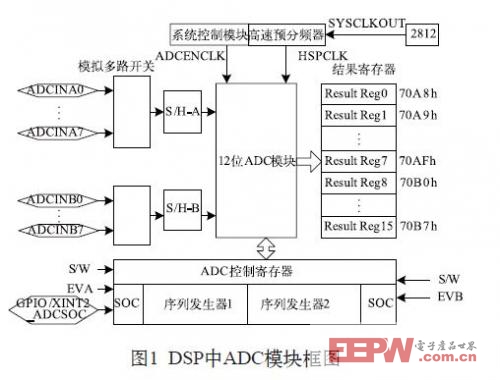

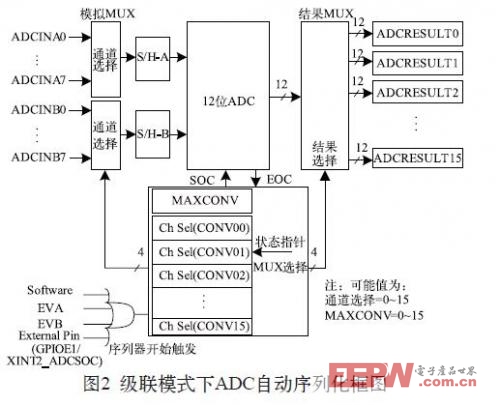

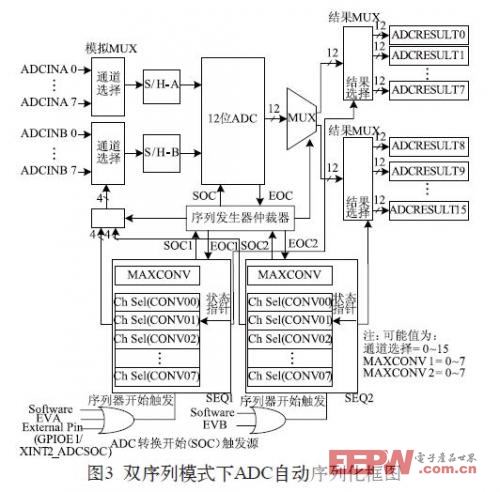

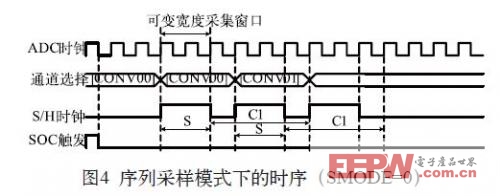

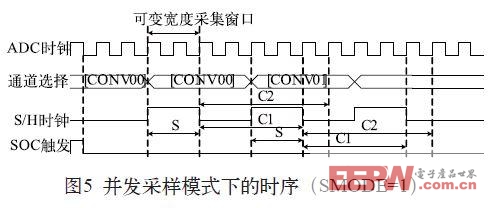

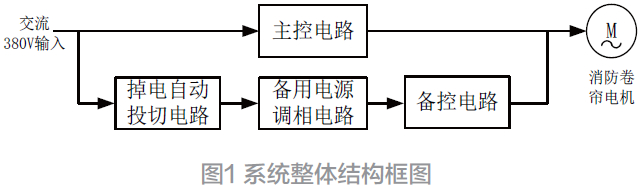

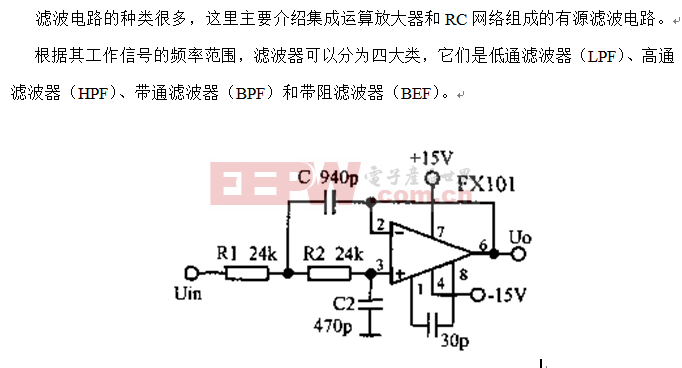

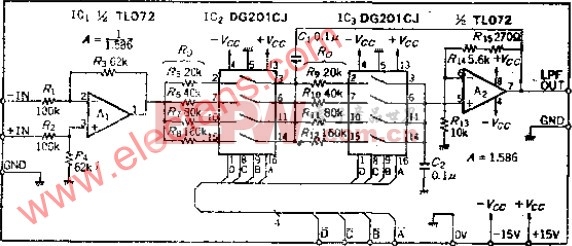

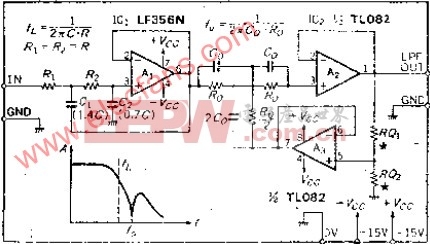

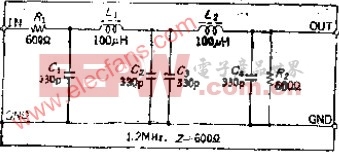

LTCC滤波器的设计通常是基于经典滤波器设计理论,从结构上讲,主要有两种结构,一种是采用传统的LC谐振单元结构,谐振单元由集总参数的电容电 感组成,另一种是采用多层耦合带状线结构。本文所设计的低通滤波器采用第一种集总参数形式,理想化低通滤波器电路原理图如图1所示。

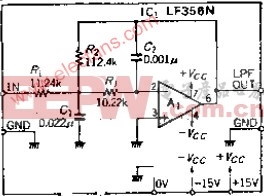

首先根据低通滤波器理想电路原理图选定实际需要的元件值,通过ADS仿真软件对电路模型进行优化,使电路仿真结果满足需要。低通滤波器原理图仿真结 果如图2所示。根据公式计算得到其基本物理结构图,然后在HFSS软件里画出物理结构,设定基板的介电常数、划分网格、设置扫描频率,仿真后得到S参数。 低通滤波器的截止频率为900 MHz;通带插损小于1 dB;通带内端口驻波小于1.5;带外抑制大于35 dB,@1.5 G.

本文设计的LTCC滤波器中的集总参数的电容和电感通过LTCC多层陶瓷集成在陶瓷基板内部。LTCC内埋植电容的设计一般采用两种方式:垂直交指 型(VIC)电容和金属-介质-金属(MIM)电容。本文设计的滤波器的内埋置电容元件采用垂直交指型(VIC)电容,在相同电容量的情况下,VIC 结构电容相比MIM结构电容能够大大减小端电极面积,从而有效减小滤波器尺寸。

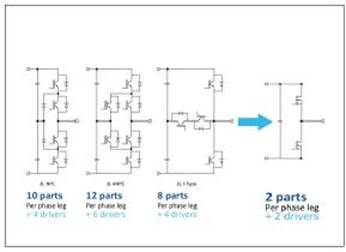

LTCC内埋电感有平面螺旋电感、堆栈螺旋电感、多层螺旋电感等方式,如图3所示,本文设计的低通滤波器内埋植电感元件采用多层螺旋结构的电感,在相同的有效电感值下此结构比平面螺旋式、堆栈螺旋式等结构具有更高的自谐振频率和品质因子。

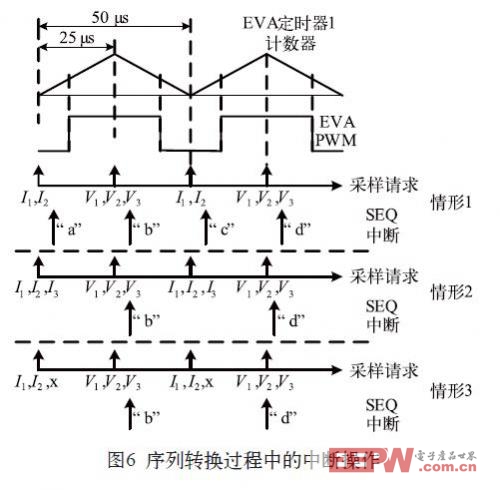

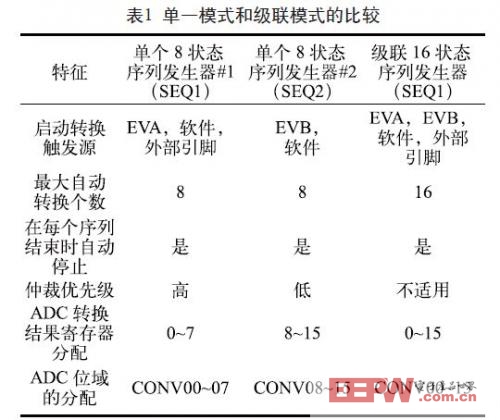

滤波器的制作采用杜邦951生瓷片,电容和电感采用配套的印刷浆料,基板介质材料相对介电常数为7.8,介质损耗为0.006,共用到14层生瓷 片,其中第3层到第8层为多层螺旋结构的电感,第9层到第12层为垂直交指型(VIC)电容,第13层为电路的地层,烧结后的器件尺寸为3.2 mm×1.6 mm×1.4 mm,滤波器的LTCC三维物理模型如图4所示。使用HFSS软件对低通滤波器模型进行三维电磁场仿真,该模型的三维电磁场仿真结果如图5所示。

3 版图设计

版图设计是按照LTCC设计规则和电路原理图完成电路中导线导体、焊盘、电极以及通孔等要素的目标尺寸设计,并完成图形文件的数据输出。LTCC版 图需要输出的数据有:光绘制版数据、冲孔数据、探针通断测试数据。还需要根据不同生瓷材料的烧结收缩因子对共烧层的光绘制版数据和冲孔数据进行收缩因子的 倒数倍放大、联片拼图等制作。

例如杜邦951PT平面收缩率为12.7%,平面尺寸1÷(1-0.127)=1.145个单位的生瓷坯经共烧后收缩为1个单位的基板。所以,所有共烧层均按1.145:1比例放大,并将电路版图联片拼图后输出光绘、制版和打孔的图形数据文件。

文中设计的低通滤波器采用200 mm×200 mm尺寸的生瓷材料进行打孔、填孔、丝网印刷、叠片、层压等工艺加工,LTCC版图数据需要拼成200 mm×200 mm尺寸的联片。联片制作示意图如图6所示。

4 关键工艺研究

LTCC工艺最大的难点在于工艺参数的敏感性、加工结果的非直观性和烧结后基板的不可返工性。对于具体的产品基板,因材料、尺寸、层数、结构、图形 分布、后烧状态等的不同,往往需要通过多轮次的实际产品加工参数调整与渐进优化,才能得到很满意的LTCC基板,尤其是烧结、层压的工艺参数,对基板的质 量影响很大。期望获得合格、高质量、高性能的LTCC基板,除了严格控制各个加工工序的材料、环境、参数、过程外,还必须在叠片前检验剔除不合格的生瓷片 层,在烧结后监控基板的收缩率、密度、强度、平整度、通断状态等关键指标.

4.1 通孔填充和印刷

在LTCC工艺中,通孔填充主要是为了层间电路连接,在生瓷片上形成的通孔中填满导电浆料。此外,在某些高频的电路设计中,还需要屏蔽孔,起到电磁 屏蔽的作用。LTCC设计中通常使用0.1 mm、0.15 mm、0.2 mm三种规格的通孔作为信号通孔。由于在工艺流程中会产生一定的误差,使用过小的通孔会导致层间互联通孔的连接变差,如果通孔直径大于0.3 mm或者小于0.15 mm,金属化时都很难形成盲孔或者埋孔,从而降低了基板的成品率和可靠性,所以通常设计中尽量避免使用小于0.1 mm的通孔作为层间电气连接的信号通孔。本文中设计的滤波器中都采用0.2 mm的通孔。填充工艺中出现的问题主要有两种,一是填充浆料过多,浆料溢出漫延会对产品的性能和可靠性造成影响,甚至造成电路短路,导致产品失效;另一种 是填充不饱满,造成层间连接失效。在微孔填充工艺中,根据生瓷片厚度以及填充浆料的特性,通过反复的实验,选择合适的填充压力和加压时间,最终取得良好的 填充效果,如图7所示。

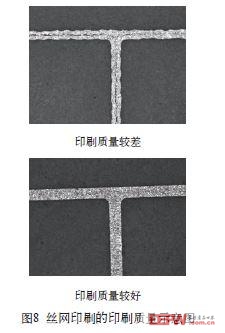

印刷是将设计好的电路图形转移到生瓷片的过程,在LTCC工艺中一般采用丝网印刷的方式将导体浆料印刷在生瓷片上。印刷是LTCC工艺中重要的一个 环节,印刷质量直接关系到最终电路的电性能,同时印刷也是LTCC工艺中最难控制的工艺环节,因为印刷质量和很多因素有关,主要包括:

(1)丝网规格;

(2)印刷过程条件;

(3)导体浆料特性;

(4)丝网特性。

好的印刷质量主要是指印刷图形位置准确、浆料量适中、形状正确、印刷稳定等。在滤波器电路图形的印刷过程中,开始容易出现印刷效果差的情况,通过不 断的改进,在丝网印刷过程中优化控制好刮板压力、印刷速度、折距等工艺参数,得到较好质量的印刷图形。丝网印刷的印刷质量如图8所示。

4.2 叠片和层压

叠片是将印刷和填孔后的单个生瓷片通过校位叠片后进行热压,使多张生瓷片结合成为一体,叠片的精度是保证三维电路连接准确不可或缺的工序,叠片精度 差会造成层间电路的互连错位,从而影响电路的性能,甚至使得电路失效,如图9所示。在早期的LTCC工艺中较多使用手工叠片的方式,随着LTCC电路印刷 线路和通孔尺寸的缩小,手工叠片对位的精度逐渐满足不了工艺要求,现在普遍采用自动化的叠片设备,主要由CCD摄像头、一个XY-θ平台和一个固定平台组 成,通过校准生瓷片上的对位孔和摄像头的中心轴,作为对位的标准光轴,将生瓷片放在XY-θ平台上并调整位移和角度,使对位孔中心和标准光轴重合,从而达 到精确对位的效果,目前自动化叠片设备的层间对位精度可以达到10 μm以下。

层压是将叠片完成的生瓷片通过单轴压或者等静压,使其成为致密的整体,本文中滤波器制作工艺中采用等静压的方式,先将叠片完成的生瓷片真空包封在防 水的袋中,然后放入等静压层压机的压力水腔进行层压。层压的基本参数是压力和温度,本文中使用的工艺条件为压力21 MPa,层压温度70 ℃,先预热5 min,然后升压至层压压力,层压时间13 min.层压过程中最大的问题是分层,分层会导致基板烧结后产生分层断裂和缺陷变形。为了防止分层现象,需要根据产品的特性优化层压的条件,包括压力、温 度、时间等参数。

5 结论

本文设计了一种小型化的LTCC低通滤波器,通过对滤波器原理图的分析和仿真,建立了低通滤波器三维电路物理模型并完成三维电磁场仿真,滤波器采用 集总参数形式的多层螺旋结构电感和VIC电容设计,采用14层生瓷片结构,尺寸面积为3.2 mm×1.6 mm×1.4 mm.重点分析了LTCC低通滤波器电路版图设计和工艺流程中的一些关键问题,并在LTCC工艺线上完成滤波器的加工,滤波器电路的实物图如图10所示。 900M小型化LTCC低通滤波器可广泛应用于无线移动通信系统中。

低通滤波器相关文章:低通滤波器原理

电源滤波器相关文章:电源滤波器原理

功分器相关文章:功分器原理

评论