ADC中的输入采样结构

当今的模拟系统设计人员面临许多设计挑战。他们不仅需要选择合适的集成电路(IC)器件,还必须准确地预测这些元器件在系统内的相互影响。由此看来,模数(A/D)转换器的设计是一项艰巨的挑战,因为必须在系统级考虑各种不同的输入采样结构,并做出正确的选择。本文将探讨几种通用的输入采样结构,并讨论每种结构对系统其他部分的影响。

本文引用地址:http://www.amcfsurvey.com/article/258787.htm输入采样基本电路结构

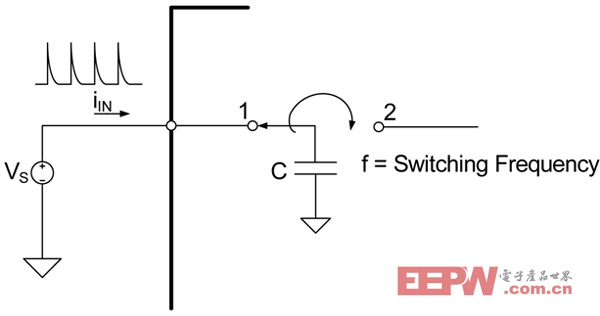

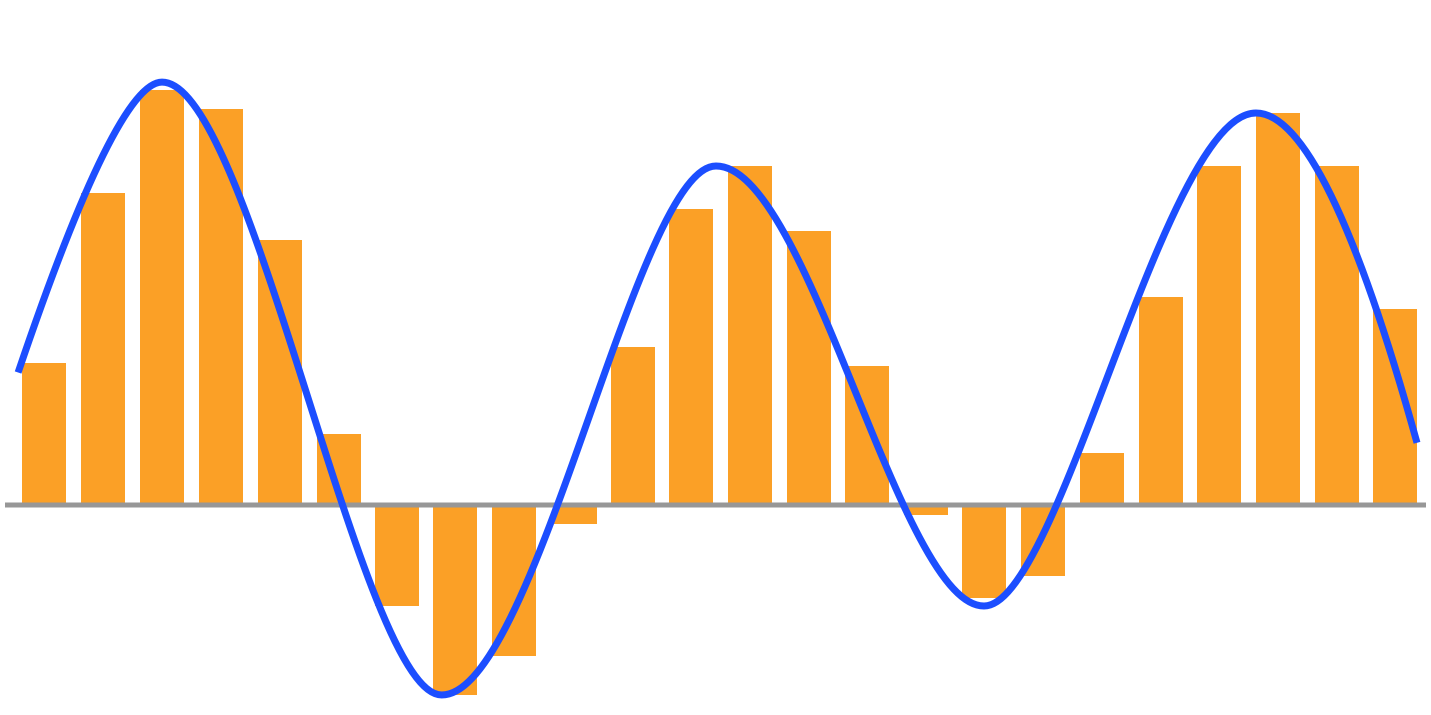

随着数字化的普及和技术的发展,A/D转换器的应用无处不见。在目前使用的众多CMOS A/D转换器中,一种常用解决方案是使用开关电容结构实现输入采样。在这种最基本的结构中,输入部分由一只体积相对较小的电容器和一个模拟开关组成,如图1所示。

当开关设在位置1时,进入采样过程,采样电容器被充电至采样节点的电压(在此例中为VS)。然后,开关被切换至位置2,转换到放电过程,此时采样电容器上累积的电荷被放电或转移至采样电路的其他电路上。充电,然后放电,再充电,再放电,这一过程周而复始。

上述电路结构中,没有使用缓冲器,而是直接利用开关电容器输入,这样会引起严重的系统级问题。因为在采样过程中,将采样电容器充电到采样点电压所需的电流必须由连接到A/D转换器输入端的外部电路来提供。当电容器切换到采样节点(图1中的开关位置1)时,需要大电流对电容器进行快速充电。实际上,这一瞬态电流的大小是采样电容器容值、电容开关频率和采样节点电压的函数。

该开关电流由下式表示:

iin = CVf

其中,C为采样电容器的电容值,V为采样节点上的电压(此例中为VS),而f为采样开关的开关切换频率。这个开关电流会在采样节点产生较高的电流过冲峰值(如图1所示)。

图1 简单的开关电容输入结构

在对A/D转换器的前端模拟电路进行设计时,必须考虑这一开关电流所带来的不良影响。当该电流流经任何电阻时,都会产生压降,从而在A/D转换器的采样节点处产生电压误差。如果转换器的输入端连接有高阻抗传感器或高阻抗滤波器,那么误差将变得很大。

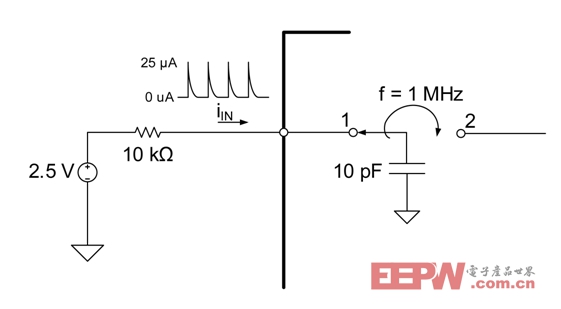

为了进行详细的说明,引用一个例子,如图2所示。该例中假设A/D转换器的前端加有一个阻值为10kΩ的电阻,来隔离传感器并改善静电放电(ESD)保护功能。

图2:带串联电阻的无缓冲开关电容输入

此例中采样电容器为10 pF,开关频率为1 MHz。根据上式,瞬态电流约为25 µA。当这个瞬态电流通过输入端串联的10 kΩ电阻时,采样节点上将会产生250 mV的电压误差。由于采样点可能在下一个采样周期之前达到稳定,因此这是最差情况下的估算值。具体的充电环路的建立时间取决于10 kΩ电阻器和采样电容以及A/D转换器输入端的寄生电容所构成的RC时间常数。寄生电容来自于A/D转换器的连接导线、电路板走线长度以及内部MOS开关电容等。此外,可能需要外部缓冲器电路提供必需的电流,并确保采样点得到正确设置以保持线性。然而,在更高开关频率下,放大器输出阻抗会增大。因此必须仔细选择放大器和相关电路才能解决瞬态开关电流问题。

输入采样改进电路结构

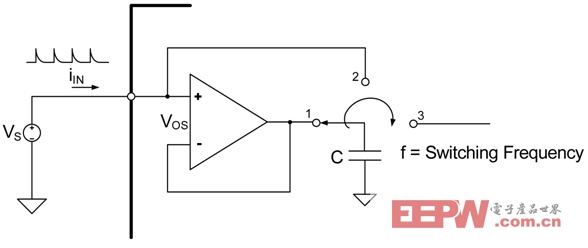

为尽可能减小外部电路所必须提供的大充电电流,以及因为开关高速切换所导致的瞬态电流过冲对系统带来的不利影响,对图1所示的基本电路结构进行了改进,具体改进电路如图3所示。通过比较可以发现,改进后的电路在采样电容之前加入了一个内部缓冲器。

图3:带缓冲的开关电容输入

加入内部缓冲器后,模拟开关可组合成三种不同的状态。在位置1处,采样电容器被快速充电至采样节点电压(VS)加上或减去(具体视偏差电压的极性而定)缓冲器电压偏差(VOS)。在此阶段,电容器充电所需的瞬态电流不再由外部电路提供,而是由内部缓冲器电路提供。对内部缓冲器进行优化设计,可使其在所要求的开关频率下提供低输出阻抗,以便在指定的充电时间内给电容正确地充电。然后,重新设置开关,使其连接到图3中的位置2处。此阶段采样电容器直接连接到A/D转换器的采样节点。接着,采样电容器被充电或放电,以便电容器电压与采样节点电压相等。这时可能仍然存在少量开关电流,但所需的外部电路电流较小,因为电容器电压已经被充电至内部缓冲器的偏置电压范围内。这种方案的关键是,必须精确计算开关被设置到位置1处的预充电时间,以避免该充电时间过长,从而造成过充电进而对输入端的外电路反向放电。

最后,模拟开关切换到位置3,将采样后的电压传送至采样电路的其余部分。这一阶段与图1所示的基本结构完全一样。

通过比较发现,带缓冲电路的开关电容输入结构的优点是能够大幅减少对A/D转换器外部电路所需提供的瞬态电流。前面的例子中采样电容器为10 pF,开关频率为1 MHz。假设内部缓冲器电压偏置为10 mV,通过合理控制预充电的时间后,最终在与外电路相关的充电阶段所产生的瞬态电流仅100 nA,比不带缓冲的采样输入瞬态电流小250倍。

输入缓冲器的进一步优化

有些情况下,可将一个固定或可编程增益放大器集成到A/D转换器前端的器件中。集成的放大器不仅有助于减小必须由外部电路提供的开关电流,而且还能对模拟信号进行放大。此外,还可采用一个斩波稳定放大器来减小1/f噪声,即所谓的“闪烁噪声”。这种低频噪声是生产工艺固有的MOS晶体管通道表面状态引起的。斩波可以消除1/f噪声,并减小外部电流要求。然而,由于MOS开关的不匹配,电路中仍将存在少量输入瞬态电流。

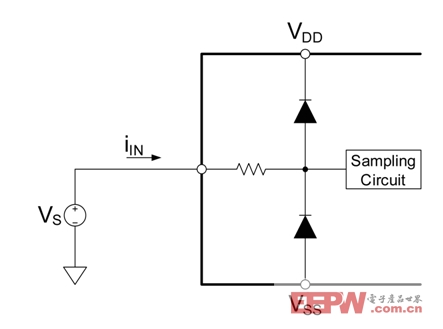

无论是何种采样结构,A/D转换器都必须采取ESD保护。对于CMOS方案来说,一般采用钳位二极管提供ESD保护,如图4所示。钳位二极管可有效限制加在转换器内部晶体管上的电压。如果输入电压与电源轨的差值超过二极管压降(通常为0.7V),则二极管将导通,从而起到限制电压的作用。但钳位二极管同样会出现电流泄漏,在设计模拟输入电路时必须考虑这个问题。尽管这一泄漏电流通常较小,也许只有几皮安,但该电流会随着温度升高而大幅增加。

图4:CMOS ESD保护

结论

随着A/D转换器的不断发展,系统设计人员充分理解所采用的输入结构以及这种结构对外部电路的影响变得越来越重要。本文讨论了一个简单的开关电容输入结构。开关电流要求会对系统的整体性能产生巨大影响,因此必须合理设计外部电路。集成的缓冲器或放大器可大幅减小开关电流,简化A/D转换器外部电路设计。ESD保护电路也会影响外部电流要求,并且其影响随温度会有很大的变化。

作者:高级产品市场营销工程师Kevin Tretter

Microchip Technology公司模拟和接口产品事业部

评论