SHARC处理器满足一高二低的浮点设计需求

浮点DSP比定点DSP的动态范围更大;很多算法的浮点代码比定点占用更少的周期;浮点DSP可以实现更高的精度;浮点DSP的浮点运算用硬件来实现,其处理速度大大高于定点DSP…...这些浮点DSP与定点DSP的比较优势是浮点算法拥趸者们在“浮点定点之争”的话题中常提及的,也为大多数嵌入式设计工程师所熟知。

本文引用地址:http://www.amcfsurvey.com/article/257966.htm然而,由于电路复杂性和制造工艺上的原因,浮点处理器与定点处理器相比在成本和功耗上通常具有明显的劣势,从而导致浮点处理器的卓越处理能力、大动态范围和高精度的优势一直以来成了雷达、专业音频、医疗设备等高端产品的“专利”。近年来,浮点处理器在提供高性能的同时,在降低功耗和成本上有了长足的进步,主要的提供商都提供了5到10美元以内的浮点DSP,功耗也显著降低,浮点处理器正在开启更广泛应用的大门。

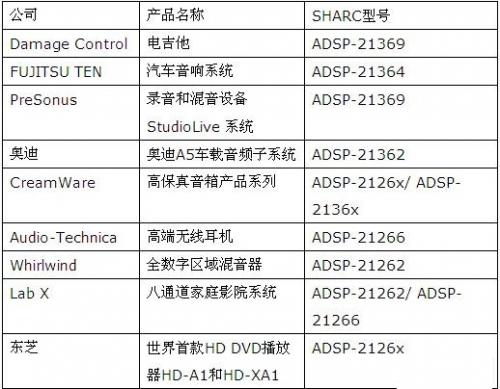

近日,浮点处理器全球领导企业ADI公司推出了其第四代SHARC处理器的新系列——ADSP 2148x和ADSP 2147x,在延续第四代SHARC处理器的高性能基础上,新型处理器在低成本和低功耗特性上具有不俗的表现,将为成本和功耗敏感的产品带来利用浮点DSP的机遇。本文将解析新型SHARC处理器的“一高”(高性能)、“二低”(低功耗和低成本)特性,以及将给便携式电子、消费电子等产品设计带来的技术应用创新机遇。

“一高二低”的浮点DSP新典范

从第一款真正的SHARC处理器ADSP-21060在16年前推出以来,SHARC处理器就一直引领着高性能浮点处理器的技术标杆。ADSP 2148x和ADSP 2147x处理器继承了第四代SHARC处理器的优良“基因”并实现了多项创新:具有PCG、8个串口、4个立体声通道ASRC、UART、TWI,可为工业、仪表、消费类音响、汽车和专业音响应用提供理想的外设特性;采用可变指令集架构(VISA),可以通过缩减指令操作码大小为应用代码释放多达30%的存储空间;最高5Mb片上RAM容量支持单芯片解决方案,允许许多应用取消外部存储器元件,而且每Mb的价格只有竞争性器件的一半,从而降低系统BOM成本;滤波器硬件加速器允许并行执行,能为内核释放出更多的MIPS;具有专用的硬件加速器和独立的计算单元以及DMA控制器,实现了后台执行FFT/FIT/IIR信号处理,可减轻内核处理负担;等等。SHARC2148x和SHARC2147x除了具有上述共同特性外,还分别针对各自的目标应用进行了若干优化,使其更加符合特定目标应用的性能、成本、集成度和功耗要求。

高性能、低成本是ADSP 2148x系列处理器的主要特点。最高400MHz的性能比同类32位竞争DSP产品提高33%,芯片支持滤波器功能使其执行滤波运算时不耗用内核资源,从而进一步提高处理能力。针对工业和汽车应用,SHARC2148x系列部分型号还集成了热敏二极管以支持高环境温度工作。对于某些需要大容量存储器的应用,集成的内存控制器可直接连接SDRAM、闪存和SRAM。而ADSP 2148x价格低至9.49美元。

图1:SHARC2148x和2147x处理器内部功能框图

低功耗是新款SHARC2147x系列处理器的最大亮点,在最高266MHz的性能条件下功耗仅为363mW(典型值),比同类竞争处理器功耗降低达20%。SHARC 2147x系列处理器充足的片上存储器和先进的并行处理能力都有利于降低功耗,通过扩展处理器的低功耗架构,确保系统级功耗的大幅节省。这些功能使设计师能够满足苛刻的功率预算。

评论