McBSP在数据传输中的应用

DSP芯片主要完成数字信号的采集、存储、处理与传输的任务。多通道缓冲串口(McBSP)是最重要的数据采集和传输设备之一,是一种典型的可配置外设,通过对其接口参数和数据格式的编程设定,可以实现对具有同步串行口的编码器等外部IC芯片的无缝连接。这里将以TMS32 0VC5502DSP和TLV1572模数转换器为例介绍DSP的多通道缓冲串口(McBSP)在数据传输中的应用。

本文引用地址:http://www.amcfsurvey.com/article/257783.htm1 硬件构成

1.1 TMSC320VC5502

DSP芯片采用TI公司的TMS 320 VC5502,它是一种高性能、低功耗、定点数字信号处理器,它主要有以下特点:

1)最高主频能够达到300 MHz,指令周期3.33ns。

2)包括1条32位的程序数据总线,5条16位的数据总线,6条24位的程序地址总线。这种并行的多总线结构,使CPU能够在一个CPU周期内完成一个32程序代码的读、3个16位数据的读和2个16位数据的写。5502还拥有2个乘法累加器,每个累加器都能够在一个周期内执行一个17x17 bit的乘法运算。

3)包含28kx16bit的片上ROM,包括64kBytes的DARAM(8块,每块4 kx16 bit),192 kBytes的SARAM(24块,每块4 kx16 bit)、64 kBytes的一等待片上ROM(32 kx16 bit)和最大可寻址8 Mx16 bit的外部存储空间。16位的外部存储器扩展接口可实现与异步存储器件(SRAM、EPROM)和同步存储器件(SDRAM)的无缝连接。

4)片上外设包含1个六通道的直接存储器访问控制器(DMA)、3个多通道缓冲串行口(McBSP)、1个可编程的数字锁相环时钟发生器、2个64 bit通用定时器、1个64 bit看门狗定时器、1个64 bit DSP/BIOS计数器、8 bit/16 bit主机接口(HPI)、7个通用输入输出口(GPIO)和1个外部标志输出引脚(XF)、1个内部集成电路模块(I2C)、1个通用异步接收/发送器(UART)、1个符合IEEEl941.1标准(JTAG)边界扫描逻辑的JTAG仿真接口。

1.2 McBSP(多通道缓冲串口)

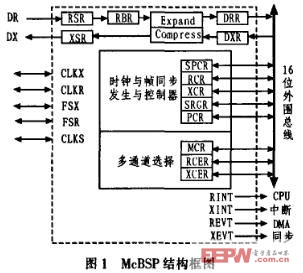

TMS320VC5502 DSP提供了3个高速多通道同步缓冲串口(McBSP),使得TMS320VC5502DSP可以直接和其它C55xDSP、多媒体数字信号编解码器以及系统中的其它设备接口。该串口提供了全双工通信;双缓冲数据寄存器,允许传送连续的数据流;独立的收发时钟和帧信号:可与工业标准的编解码器、模拟接口芯片及其它串行A/D、D/A芯片直接连接;可用128个通道进行收发;具有可编程的采样率发生器;能够向CPU发送中断,向DMA控制器发送DMA事件;可设置帧同步脉冲和时钟信号的极性;传输的字长可以是8位、12位、16位、20位、24位或32位;可将McBSP引脚配置为通用输入输出引脚。McBSP结构框图如图1所示,可以分为数据通道和控制通道2部分。

数据发送引脚DX负责数据的发送,数据接收引脚DR负责数据的接收,发送时钟引脚CLKX、接收时钟引脚CLKR、发送帧同步引脚FSX和接收帧同步引脚FSR提供串行时钟和控制信号。CPU和DMA控制器通过外设总线与McBSP进行通信。当发送数据时,CPU和DMA将数据写入数据发送寄存器(DXR1,DXR2),接着复制到发送移位寄存器(XSR1,XSR2),通过发送移位寄存器输出至DX引脚。同样当接收数据时,DR引脚上接收到的数据先移位到接收移位寄存器(RSR1,RSR2),接着复制到接收缓冲寄存器(RBR1,RBR2),RBR再将数据复制到数据接收寄存器(DRR1,DRR2)中,并通知串口事件通知CPU或DMA读取数据。这种多级缓冲方式使得片内数据通信和串行数据通信能够同时进行。

1.3 TLV1572

A/D转换器用TI公司的10位高速串行逐次逼进型A/D转换器,采用5 V单电压供电,最高采样速率可达1.25 Msps,可与TMS320系列DSP通过McBSP(Multi-channel Buffered Serial Ports,多通道缓冲串口)实现无缝连接。TLV1572的采样速率最高可达1.25 Msps、10位分辨率、单电压供电是3~5V、低功耗(3 V时8 mW、5 V时25 mW)、自动节电功能(最大电流为10μA)、具有内部采样保持功能。TLV1572的功能模块图如图2所示。

TLV1572有2种工作模式,即DSP模式和微控制器模式,这2种工作模式是由它的P3(帧同步输入信号)的电平决定的,FS引脚连接电源VCC,一直为高电平,则TLV1572工作在微控制器工作模式下;如果TLV1572在DSP工作模式下,则FS引脚或者由TMS320 DSP的MCBSP的帧同步信号(FSR)提供,或者由系统外部引入。

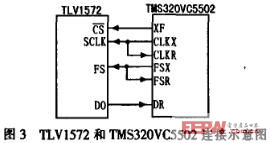

1.4 TLV1572与DSP的McBSP缓冲串口的连接

TLV1572与TMS320VC5502 DSP串口连接如图3所示。

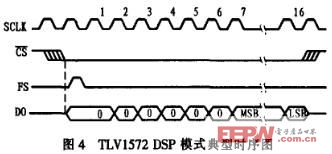

TLV1572工作在DSP模式下,其典型时序图如图4所示。

在DSP模式下工作时,当TLV1572 A/D的片选信号/CS变低时,FS也必须为低,而且为了确保TLV1572的DSP模式的正确锁定,FS信号电平要被检测2次,一次是在/CS下降沿时检测FS电平(也就是对于/CS下降沿的FS建立时间,最小6 ns),一次是紧接其后的相对于/CS下降沿来说的一个内部延迟检测(也就是对于/CS下降沿的FS保持时间,最小为9 ns)。综上所述,为了保证TLV1572能正确锁定在DSP模式下,在/CS变低后FS要至少维持15ns的时间。

在确保TLV1572工作在DSP模式下后,也就是FS的低电平至少要维持15 ns的时间后,TLV1572 A/D要在每一个SCLK时钟信号的下降沿检测FS的电平状态,一旦FS变高,说明A/D进入复位状态,之后当FS变低时,TLV1572等待DSP锁存第一个0。这里,FS的上升沿对于对SCLK的下降沿来说有一个FS的建立时间(至少10 ns),然后相对应这个SCLK的下降沿,FS有一个保持时间(至少要4 ns)。满足至少上述的14 ns后,FS才能变低。

采样从FS变低后的第一个SCLK的下降沿开始,一直到输出第6个0时的那个SCLK的上升沿,在这个SCLK的上升沿,开始转换并输出相应转换的数据,这里有1 bit的延迟,而DSP对转换数据的采样发生在SCLK的下降沿。经TLV1572转换的数据前导有6个0,之后才是转换的由高位到低位的10 bit数据输出。也就是说TLV1572对一次的数据完整转换需要16个SCLK。如果在第16个SCLK时钟的下降沿检测到FS变高了,则在即后的下一个SCLK,也就是第17个SCLK开始下一次的新的数据的采样与转换,这样就实现了TLV1572的对数据的连续转换。

2 软件构成

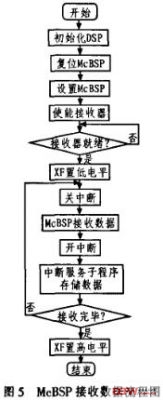

当所传输的信号从TLV1572的模拟信号输入端输入后,TLV1572再对输入的信号进行采样,并将采样后的数据传送到DSP。程序主要包括初始化DSP和缓冲串口McBSP,将McBSP配置为接收器,包括复位MeBSP的接收器,根据需要对McBSP的寄存器编程,使能接收器,启动A/D,采集数据并存储,其流程如图5所示。

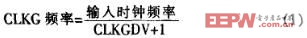

在对DSP的McBSP进行操作时,McBSP的内部采样率发生器的输出时钟CLKG驱动给CLKR,CLKR同时提供给A/D的SCLK。而McBSP的采样率发生器的时钟源(CLKSRG)由CPU提供的,对CPU时钟进行分频以产生CLKG。由于CPU的时钟极性总为正,因此CPU时钟信号的上升沿产生CLKG的上升沿。对采样率发生器的寄存器编程后,要等待2个CLKSRG(时钟源)周期以确保内部同步。当采样率发生器使能后,要等待2个CLKC周期,以保证采样率发生器稳定工作。在CLKSRG的下一个上升沿,CLKRG变为1,启动频率如式(1)所示的时钟。

帧同步信号(内部FSR),对于串口来说,都是内部信号,都是高电平有效。如果将串口配置成外部帧同步(FSR输入到McBSP),且FSRP=1(接收帧同步信号低有效),则外部低电平有效的信号在送给接收器(内部FSR)之前要做转换。当McBSP的FSR为输入时,McBSP在CLKR的下降沿检测这个FSR信号。到达DR引脚的接收数据,也在内部CLKR的下降沿采样。这里的内部时钟CLKR是由采样率发生器时钟(CLKG)驱动,内部送给McBSP。

接收器可以在时钟的上升沿可靠的对输入数据进行采样。接收时钟的极性(CLKRP)设置成采样接受数据所用的沿。注意:McBSP总是在内部CLKR的下降沿对数据采样,因此如果CLKRP=1,且选择内部时钟(CLKRM=1),则内部下降沿触发的时钟,在送给CLKR引脚输出之前,要转换成上升沿触发的时钟。

DSP的CPU或DMA控制器与McBSP的通信,是通过16 bit的寄存器访问内部的外设总线来实现的。McBSP的数据接收寄存器2个,DRR1和DRR 2,当字长小于16 bit时使用DRR1。把McBSP要传输的串行字定义成为16 bit(刚好是10 bit A/D转换数据出的6个0+10 bit二进制数),并自行定义McBSP传输数据的一帧就是16 bit。这样McBSP接收完一帧数据后,就触发中断,进行这一帧数据的存储,然后进行下一帧数据的采样转换与传输,直到数据传输采集完毕。

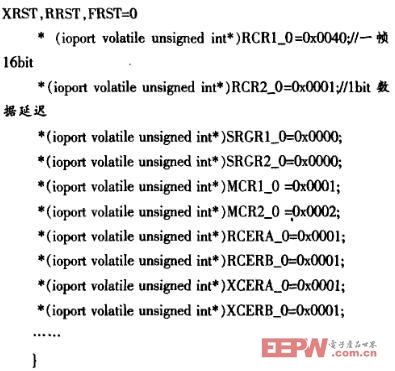

下面是MeBSP配置成接收器要做的操作。

1)全局设置包括设置接收器的引脚为McBSP的引脚、使能或者禁止数字回环模式、使能或者禁止时钟停止模式、使能或者禁止多通道选择模式。

2)设置数据即选择每个接收帧是单段还是双段、设置接收字长、设置帧长度、使用或者禁止忽略接收帧同步功能、设置接收压缩扩展模式、设置接收数据延迟、设置接收数据扩展和校验模式、设置接收中断模式。

3)帧同步设置 即设置接收帧同步模式、设置接收帧同步极性、设置采样率发生器帧同步周期和脉冲宽度。

4)时钟设置即设置接收时钟模式、设置接收时钟极性、设置采样率发生器的时钟分频值、设置采样率发生器的时钟同步方式、设置采样率发生器的时钟模式(选择输入时钟)、设置采样率发生器输入时钟的极性。

调试程序所用的软件是TI公司的Code Composer Studio(CCStudio),它是TI公司开发的专用于进行TMS320系列DSP软件设计的集成软件开发环境。McBSP初始化程序如下:

3 结束语

本文以TMS320VC5502 DSP芯片与TLV1572模数转换芯片为例,详细讨论了TLV1572与DSP的多通道缓冲串口(MeBSP)通信的硬件接口和软件设计。其设计方案简单易行,具有一定的通用性,根据需要可以在中断服务子程序中嵌入适合的数据处理程序代码,就可以构成一个完整的数据采集与传输程序。本文中采集的数据是存放在TMS320VC5502芯片内部的RAM中,由于TMS320VC55x DSP的外部存储器接口(EMIF)支持8bi-t、16 bit、32 bit数据的访问,并为异步存储器、同步突发SRAM、同步DRAM提供了无缝接口,所以如果系统所要采集的数据量很大,也可以通过EMIF接口外扩存储器。

评论