基于DSP的内嵌PCI总线的卫星信号仿真器设计方案

0 引 言

本文引用地址:http://www.amcfsurvey.com/article/257561.htm卫星信号仿真器在卫星导航的研究开发中占有重要地位,特别是多模接收机和高动态接收机的研发。多模卫星仿真器中涉及到大量的数据传输,为了保证PC机和DSP之间数据传输的实时性和准确性,选择基于PCI总线接口进行数据传输。常用的PCI开发是采用专门的PCI接口芯片,但这样系统就会多一块芯片,性价比低,而TI公司TMS320C6416系列的DSP拥有内置PCI接口,使得硬件开发难度降低和主机对DSP资源访问更加透明。提出一种基于TMS320C6416系列DSP的PCI总线卫星信号发生器的硬件平台以及相应的PCI接口电路设计。

1 系统结构与实现方案

1.1 系统总体结图

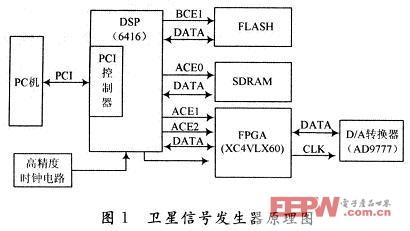

图1是仿真器的总体结构框图,其核心器件包括DSP6416,SDRRAM,FLASH,FPGA,D/A,时钟以及PC机。其中,D/A完成数字信号到模拟信号的转换;SDRAM作为外设存储器存储由PC机传来的数据;FLASH用于在系统掉电后保存DSP的运行程序;FP-GA作为仿真器的另一核心部件,主要完成与DSP的通信、信号的合成和D/A的控制;PC机主要完成仿真器的数字信号处理与计算好的数据在PCI接口和DSP间的传递。DSP作为主机和FPGA之间的通信桥梁,主要完成两方面的工作:一是定时接收PC机计算的各种控制字和电文,按照时序要求,将各通道的控制字发送给FPGA;二是由于PC机计算是双精度浮点型的,而FPGA中只能以整型数据计算,这样必然会造成两者相位累加值的差异,随着时间的流逝,误差会越来越大,必须加以校正;但如果要将FPGA累加的数据再返回到PC机进行比较校正,在实时性上得不到保证,因此需要在DSP中实现对频率字的校正。

在设计中,将SDRAM作为DSP的片外存储器,配置在EMIFA的CE0空间内,FPGA与DSP通过EMI-FA接口交互数据,它配置在EMIFA的CE1和CE2空间内。EMIFB的CE1配置成异步8位通信方式与FLASH通信。

1.2 DSP与PCI接口电路连接设计

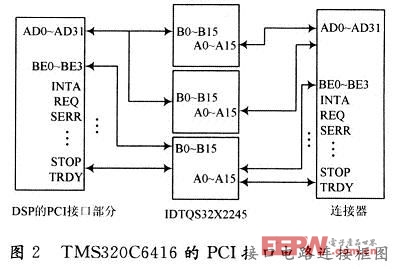

由于DSP TMS320C6416内部集成PCI接口,所以不需要桥接芯片,只需要设计与PCI母板之间的接口,不需要设计PCI与DSP本身之间的接口。由于仿真器是一个多电源系统,可以提供5 V,3.3 V,12 V的电源,所以对连接器采用多电源供电。此外,由于DSP是3.3 V系统,虽然它的PCI口能承受5 V电压,但考虑到系统的稳定性,在DSP的PCI口和连接器之间加3个电压转换芯片IDTQS32X2245,将5 V电压转换成3.3 V电压。由于DSP是集成的PCI接口,其电路设计较简单,将DSP PCI接口的地址和数据总线直接连到IDTQS32X2245芯片的B管脚部分,将铜手指上的地址和数据总线连接到IDTQS32X2245芯片的A管脚部分,仲裁信号REQ,GNT、错误报告信号PERR,SERR、字节使能信号C/BE[3:O]、接口控制信号FRAM,IRDY,STOP, IDSEL,DEVESEL也都按相同的方法连接在相应的位置上。限于篇幅,这里仅给出DSP PCI接口部分与连接器的连接示意图,如图2所示。

2 DSP6416内嵌PCI关键寄存器及其中断机制

DSP6416的PCI接口支持通过主/从总线接口连接DSP到PCI主机,PCI接口端通过EDMA内部硬件与DSP相连,它支持四种类型PCI数据交换:从模式读,即外部PCI主设备通过PCI接口写数据到DSP;从模式写,即外部PCI主设备通过PCI接口从设备读数据;主模式读,即DSP主设备通过PCI接口读数据到外部PCI从设备;主模式写,即DSP主设备通过PCI接口写数据到外部PCI从设备。

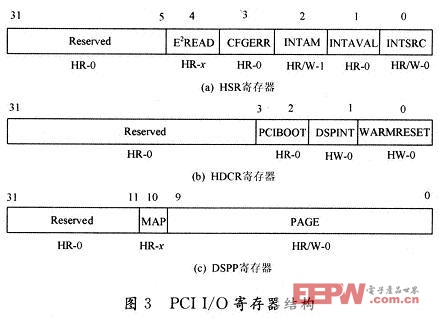

PCI寄存器主要包括3类:PCI配置寄存器、PCII/O寄存器、映射在DSP存储空间作为外设的PCI寄存器。前两类寄存器只能被外部主机访问,而第三类寄存器可以被DSP和外部PCI主机访问。

PCI配置寄存器包含标准的PCI配置信息(设备标识,厂商标识,分类代码,基址等);PCI I/O寄存器位于PCI主机的I/O空间,主机只能在:Base1和Base2访问它们,PCI I/O寄存器包括HSR,HDCR,DSPP。如图3所示,HSR寄存器表明主机的状态,它的INTSRC位和INTAM位对于中断处理至关重要。 INTAM位为1时,它可以屏蔽DSP发送的中断,当该位为0时,只要。DSP设置RSTSRC字段中的INTREQ位时,可以使能PINTA,即主机在这时可以响应中断。当INTSRC位读为0时,表示PINTA自上次清除后无效,当读为1时,表示PINTA处于使能状态,该位写0无效,写1清除 PINTA的使能状态。对于HDCR来说,PC机通过将DSPINT位置1产生主机中断。DSPP主要和Base0一起定义一段存储空间。

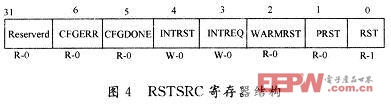

PCI内存映射外围寄存器主要用于控制PCI接口,它可以被主机和DSP访问,在该寄存器中,较重要的是RSTSRC寄存器,如图4所示。

DSP通过将RSTSRC寄存器中的INTREQ置1产生中断;PC机和DSP通过将INTRST置1清除中断,这一点在驱动开发中至关重要,因为DSP 产生的中断属于电平中断类型,如果不清除中断,它将一直有效.这将会导致中断响应函数不断的调用,从而导致死机。

评论