基于单片机和DSP的被动声目标探测平台设计方案

1 引言

被动声目标的信息一般夹杂在复杂多变的环境噪声中,信噪比低。采用传统的目标探测,较难达到要求, 必须使用先进的检测、定向定位算法,然而这些算法的运算量都较大,实时实现有一定难度。数字信号处理器DSP的出现,使得先进算法的工程实时实现成为可能。但系统的体积、功耗和可靠性又成为主要问题。本系统采用TI公司的低功耗5000系列DSP和微功耗430系列单片机,采用主从式通用化体系结构设计,在满足系统功能要求的前提下,对系统的体积、功耗和可靠性做了很大的改进,特别适于在电池供电、功耗要求严格的设备中使用。另外,对系统提供了丰富的接口,可使其满足被动目标探测系统的不同要求。

2 系统的整体设计

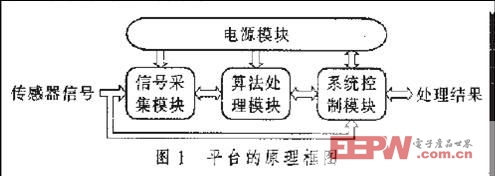

目标探测通用平台的主要功能是目标信息的获取、检测、对目标位置信息进行相应的定位算法处理和后续控制。此平台主要由4个部分组成:信号采集模块、算法处理模块、系统控制模块和电源模块。平台的原理框图如图1所示。

系统的基本工作流程是在主控单片机的控制下,先对传感器来的信号进行调理,使之满足采样要求,再由DSP控制A/D转换器对信号进行同步采样,把A/D转换后的结果送给数字信号处理器TMS320VC5509进行相应的算法处理,最后把处理结果传给主控机MSP430单片机,再由单片机去控制其他电路的工作。

其中,信号采集模块由4通道同步采样A/D转换器THS1206组成,算法处理模块由低功耗的TMS320-C5000数字信号处理器组成,系统控制模块由微功耗的MSP430单片机来实现,电源模块主要由TPS73HD-3XX系列双电压调整器来实现对整个系统的电源管理,TMS320C5000数字信号处理器工作在从机模式下,系统电源管理和从机的工作情况由主控机MSP430单片机控制。

2.1 信号采集模块

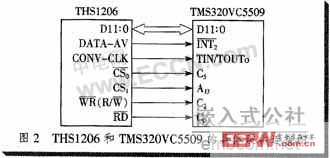

模块采用TI公司的A/D转换器THS1206。THS1206是1个可编程12 bitCMOS低功耗4通道同步采样A/D转换器,最高转换速度是6 Msample/s,最大功耗216mW,其速度、分辨率、带宽都非常适合较宽的应用方向。THS1206不需任何额外器件便可与DSP系统非常方便地进行连接。THS1206内有2个12bit控制寄存器(0,1),用来控制其工作方式(具体的工作方式可查阅参考文献[1])。一个完整的16 byte深先进先出(First InFirst Out,FIFO)存储器允许数据缓冲存储,减少了DSP中断的次数,提高了DSP的工作效率。内部参考电压范围为1.5V和3.5V。THS1206和TMS-320VC5509的具体硬件连接图如图2所示。

THS1206和DSP是通过DSP的EMIF连接的,其转换时钟信号是由DSP的通用定时器(Timer)给出的,便于灵活设置不同的采样速率。TMS320VC5509在FULL_EMIF方式下时,C0是EMIF.ARE,C2是EMIF.AWE,C5是EMIF.CE1。而片选CS1接的是A13,所以THS1206在TMS320CV5509中的地址是CE1空间和A13为高的交集。在TMS320CV5509中CE1段,其字节地址是0x400000~0x800000,再要求A13为高,所以其地址是:(xxxx,xxxx,xx1x,xxxx,xxxx,xxxxB)∩(0x400000~0x800000),则可以取字节地址为0x412000,对应的字地址是0x209000。

根据THS1206和TMS320VC5509的具体硬件连接电路,进行A/D接口初始化设置。THS1206的初始化可以查阅参考文献[1],这里着重介绍一下DSP的接口初始化配置。TMS320VC5509中外部存储器有4个片选空间,并且都可以单独进行设置,设置的内容包括存储器类型、存储器宽度、读写时序参数等。根据DSP的系统时钟(笔者设定是80MHz)和THS1206的读写时序要求,将片选控制寄存器CE1_1配置为:0x1009,即存储器类型是16bit宽异步存储器,读建立时间为0个时钟周期,读选通时间为2个时钟周期,读保持时间为1个时钟周期;片选控制寄存器CE1_1配置为:0x0009,即读延长保持时间为0个时钟周期,写延长保持时间为0个时钟周期,写建立时间为0个时钟周期,写选通时间为2个时钟周期,写保持时间为1个时钟周期;片选控制寄存器CE1_1配置为:0x0001,即禁止超时功能,在该配置下,DSP可以可靠地与THS1206进行通信。

2.2 算法处理模块

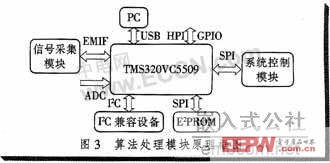

本模块主要由核心处理器TMS320VC5509组成,它是TI推出的新一代低功耗高性能16bit定点数字信号处理器,其工作主频可达到200MHz,周期效率达到了C54X的2倍,且功耗只有C54X的1/6。它还提供了丰富的外设资源,其中包括1个外部存储器接口,实现了和异步存储器如EPROM,SRAM以及同步存储器等外部设备的无缝连接;3个全双工的高速多通道缓冲串口,DSP通过McBSP可以与其他DSP,编解码器等相连;另外的外设有通用串行总线,实时时钟,看门狗定时器,I2C总线,10bitADC,多媒体卡控制器和通用输入输出接口等。在考虑充分利用DSP的外设资源的基础上,笔者设计了外扩功能完善的硬件平台,原理框图如图3所示。

基于所设计的信号处理硬件平台,设计完成了相应的驱动程序,包括:与信号采集模块连接的EMIF的接口程序,和系统控制模块通信的SPI程序,可以和PC相连的USB驱动程序,支持I2C的通信程序以及DSP集成的ADC的采样程序等。程序设计都采用模块化,便于应用程序的开发集成。基于上述软硬件平台,可以进一步开展后续开发,基本上可以满足各种目标探测算法的需求。

评论