基于DSP与串行A/D组成的高速并行数据采集系统方案

TMS320VC5402(以下简称C5402)是德州仪器公司1999年推出的定点数字信号处理器(DSP)。与TMS320C54x系列的其他芯片相比,C5402以其独有的高性能、低功耗和低价格受到了人们的广泛青睐。C5402增强外设有软件等待状态发生器、锁相环时钟发生器、6通道直接存储器访问(DMA)控制器、增强型8位并行主机接口(HPI)等。两个可编程的多通道缓冲串口(McBSP)能够全双工、快速地与其他同步串口进行数据交换,硬件连接简单,串口的工作模式和传送数据的格式可通过编程实现。

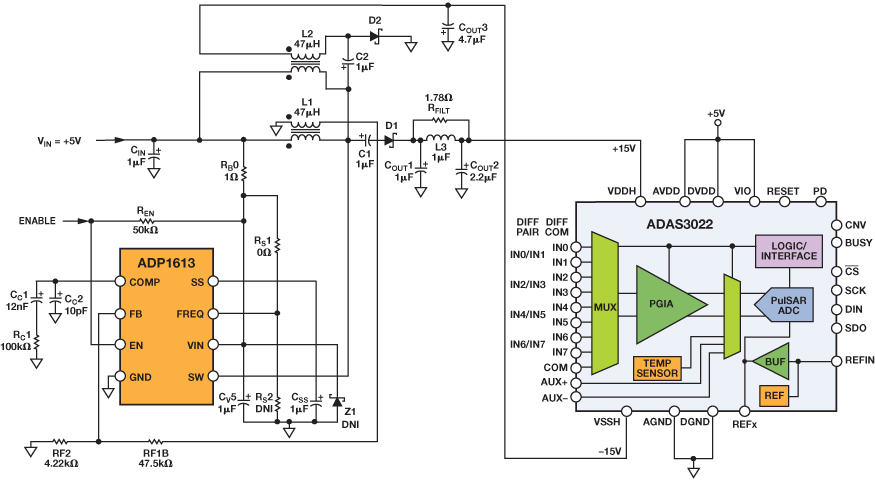

本文引用地址:http://www.amcfsurvey.com/article/257436.htm因为C5402内部没有集成A/D,因此在数据采集时需要使用A/D转换芯片,A/D芯片与C5402的接口设计成为一个重要的问题。A/D转换芯片一般有串行A/D和并行A/D。为了充分利用C5402所提供的多通道缓冲串口资源,简化系统设计,本文系统使用了TI公司的高速串行A/D来同时完成两路数据采集,大大提高了串口工作效率。

串行A/D芯片TLV1572

TLV1572是高速的十位串行A/D转换芯片,可以通过3或4个串行口线直接与DSP或其他数字微处理器串口相连,不需要外加逻辑,但是转换速度受SCLK供给时钟的限制。TLV1572与DSP的多通道缓冲串口相连是通过CS、SCLK、DO和FS四条线完成的,此时DSP的CLKR产生移位脉冲,FSR产生帧同步信号,并分别提供给TLV1572。当T-LV1572与其他串口微处理器相连接时FS必须提供高电平,通过CS、SCLK、DO三条线来完成数据传输。当CS为高时,A/D芯片各管脚处于三态状态。在CS由高变低时,TLV1572检测FS引脚的状态来确定工作模式,若FS为低则为DSP模式,若FS为高则为其他微处理器模式。

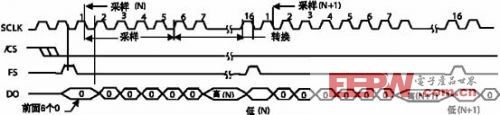

图一 TL1572在DSP模式下的转换时序图

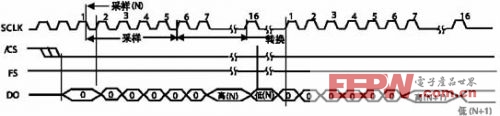

图二 TL1572在微处理器模式下的转换时序图

当TLV1572工作在DSP模式时,必须保证在CS变低时,FS为低电平,并且要锁存一定时间。CS为低时,DO跳出三态状态,但是直到FS为高时芯片才脱离休眠状态。TLV1572在每个时钟SCLK的下降沿检测FS的状态,一旦检测到FS为高,TLV1572开始采样。在FS的下降沿,A/D芯片通过移位时钟将数据移到DO上。在6个前导0传送之后,DSP可以在时钟的下降沿得到A/D转换的数据,如图1所示。在最低位移出之后,A/D芯片自动进入休眠状态,直到FS下一次有效。如果FS在16位传输完成后立即有效,则A/D开始新的数据转换,此时A/D为连续转换。若FS在TLV1572转换数据的过程中变高,则A/D芯片被复位,开始新的数据转换周期。因此可以通过设置FS,改变数据传输的位数。

当TLV1572工作在非DSP模式下时,FS引脚必须接高电平。在每次转换的过程中都必须提供16个时钟信号,若微处理器无法一次接收16位数据,可以分成8位两次接收,两次接收的时间间隔不能大于100μs,此时CS必须一直处于有效状态。在DSP模式下转换的开始是由FS信号有效来决定的,而在微处理器模式下,数据转换CS有效后的第一个时钟信号上升沿开始的,如图2所示。在微处理器模式下,也可以通过设置CS来改变传送的位数。

C5402的多通道缓冲串口

C5402提供两个高速、全双工、多通道缓冲串行口McBSP0、McBSP1,用数据线D(R/X)、帧同步线FS(R/X)和移位时钟线CLK(R/X)实现发送数据和接收数据。McBSP通过6个引脚(DX、DR、CLKX、CLKR、FSX和FSR)与外设接口。

(1)CLKX(发送时钟输入或输出)

芯片内部发送以为寄存器(XSR)通过该时钟信号将数据发送到DX引脚。该串口可以通过PCR寄存器的CLKXM位配置成使用内部时钟或者使用外部时钟。

(2)FSX(发送帧同步输入或输出)

FSX是发送开始的标志,串口可以通过PCR寄存器的FXM位配置成输入或输出。

(3)DX(串行数据发送)

串口数据发送是通过该口进行的。

(4)CLKR(接收时钟)

CLKR用来接收外部时钟信号,该时钟信号将DR数据移入接收移位寄存器(RSR)。可以通过PCR寄存器的CLKRM位配置成使用内部时钟或者使用外部时钟。

(5)FSR(接收帧同步输入)

FSR接收帧同步脉冲信号,标志数据接收开始。可以通过PCR寄存器的FRM位配置成输入,也可以配置成输出。

(6)DR(串行数据接收)

串口数据接收是通过该口进行的。接收过程中,数据首先通过移位时钟CLKR的作用下移入RSR(接收移位寄存器),然后,RSR中的数据再拷贝到DDR(数据接收寄存器),拷贝完成时,产生RINT中断通知CPU来响应或REVTA中断通知DMA响应,同时设置RRDY中断标志位,也可以用查询方式来完成,从数据寄存器中读出数据。CLKX、CLKR、FSX、FSR即可以由内部采样率发生器产生,也可以由外部设备驱动。McBSP分别在相应时钟的上升沿和下降沿进行数据检测。每个McBSP最多可支持128通道的发送和接收,串行字长可选,包括8、12、16、20、24和32位,还支持μ率和A率数据压缩扩展。

评论