基于ADSP-2106X SHARC DSPs软件仿真器的实现

本文介绍一种ADSP-2106x DSPs (数字信号处理器, Digital Signal Processors)的软件仿真器(ADSPSim)。在此仿真器构架过程中,面向对象仿真技术的使用大大改善了软件的模块化、可重用性和灵活性,更加体现了软件仿真器在实现软硬件协同设计开发和早期测试过程中的优势。

1 引言

DSPs(数字信号处理器)在航空航天工程等领域已得到广泛应用,为实现早期测试,仿真器的使用提供了建立嵌入式系统软硬件协同测试环境的可能。仿真器可分为软件仿真器(Simulator)和硬件仿真器 (Emulator)两类,而软件仿真器比较硬件仿真器有着不可替代的优势:

(1) 开发人员能在获得实际硬件原型前,能快速评价目标机软、硬件特性,实现硬件和软件并行设计开发,并缩短嵌入式软件的开发周期,尽早发现软件中的缺陷,降低开发成本;

(2) 软件仿真器具有高度的灵活性,可独立对CPU进行深入分析,或可用于对整个系统进行建模。还可轻松地进行重新配置,可与各种存储器或外设相集成。这样就可以对整个嵌入式系统的正确性进行验证。

(3) 由于软件仿真器能够反复地运行相同的仿真过程,便于在对软件进行调试、测试过程中,控制与分析应用程序运行及仿真环境的状态,并可以采集到大量的调试数据。

软件仿真器一般都是在ISA(指令集体系结构)级对系统进行仿真的,本文也不例外,也就是所说的指令集仿真器。

指令集仿真器的实现方法有两大类:一类是解释型指令集仿真器,将应用程序装载入仿真的存储器中,在运行时模拟“取指(fetch)-译码(decode)-执行(execute)”的流水对每条目标指令进行解释,将结果存入仿真的寄存器或存储器中。另一类是编译型指令集仿真器,又可细分为基于静态编译与基于动态编译两类,其原理是将目标机的指令直接翻译为能实现相应功能的宿主机上的指令/指令块,翻译在编译时实现为基于静态编译的指令仿真器,在装载时才实现为基于动态编译的指令仿真器。解释型指令集仿真器仿真速度比较慢,但由于是对指令的逐条解释,可以提供对执行应用程序的很方便的控制;而编译指令集仿真器虽然有较高的仿真速度,但由于对源程序进行了反编译后又进行了优化,已经丢失了原来的用户程序与高级语言的对应关系。解释型指令集仿真器提供了调试运行仿真器的可能,更利于嵌入式软件测试,因此本文中的指令集仿真器的实现采用此类方式。

随着面向对象技术的成熟,仿真软件已经朝着可互操作性、可重用性、面向对象的趋势发展,面向对象仿真( Object-Oriented Simulation )已成为当前仿真研究领域最为活跃的研究方向之一。本文中的软件仿真器ADSPSim在构架上也采用了面向对象的仿真技术。

2 ADSP-2106x SHARC DSPs简介

ADSP-2106x是AD公司的第二代32位浮点数字信号处理器,AD称之为SHARC(Super Harvard Architecture Computer,超级哈佛结构体系结构计算机)。目前包括四种产品:ADSP-21060、ADSP-21061、ADSP-21062、ADSP-21065L。

2.1 ADSP-2106x体系结构概述

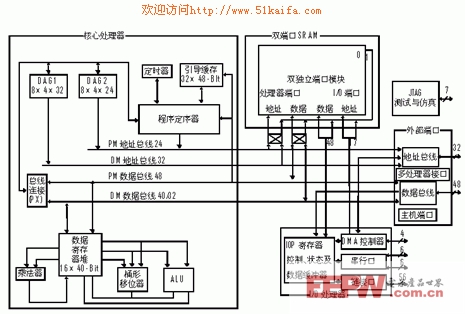

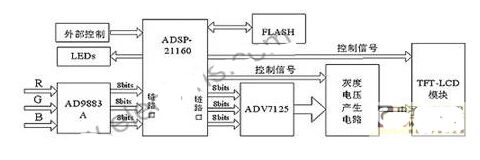

和冯诺伊曼结构不同,哈佛结构使用分离的数据和程序空间及分类的访问总线。而改进的超级哈佛结构的超级之处在于允许在程序存储器(PM)中同时存放数据和指令(可灵活配置)。再辅以独立划分的片内总线(分别用于PM和DM, 数据存储器)和指令高速缓存,很好地解决了在执行双数据存取的指令时,当需要从PM中读写数据而产生的使用PM数据总线的冲突。当第一次发生使用PM数据总线的冲突时,处理器会将指令存放在高速缓存中,当再次使用该指令时,处理器就可以一次性完成从高速缓存中取指令,从DM和PM同时取数据的并行操作。ADSP-2106x的详细体系结构如图1所示。

图1 ADSP-2106x 组成框图

2.2 ADSP-2106x指令系统概述

ADSP-2106x指令系统具有RISC(精简指令系统)指令长度一致、单周期执行时间、易于并行和流水线处理的特点,可以分为四大类:计算并存取指令,程序流控制指令,立即数寻址存取指令,及其它指令。又可按照操作码细分为24小类。值得指出的是,其中大多数指令包含指定计算操作的域。ADSP-2106x指令固定长度为48位,若包含计算操作域,则低0~22位固定为计算操作指令。详细指令集见附录AB。

正是由于计算指令与存取或跳转指令可以合并在一条指令中译码执行,ADSP-2106x拥有一个高性能的计算内核,它可以在每个指令周期内完成三个计算,包括一次加法、一次减法、一次乘法,以及寄存器到存储器的存/取操作,或是程序流的改变操作。因此在60 MHz 的时钟速率下可以得到180 MFLOPS(每秒兆浮点操作次数)的性能。

3 软件仿真器ADSPSim的构架与实现

ADSPSim在INTEL/WINDOWS 2000环境下运行,模拟SHARC体系结构的数字信号处理器,属于跨体系结构仿真,这也是采用解释型指令仿真技术的原因之一。

3.1主要功能

ADSPSim的主要功能是模拟ADSP-2106x执行其上扩展名为.dxe的可执行程序。此类目标可执行程序为 ELF(Executable and Linkable Format)格式,其中的调试信息符合DWARF2格式。除了模拟核心处理器基本功能外,ADSPSim还能仿真了双端口SRAM,IOP(I/O Processor)寄存器等。

除了模拟功能外,ADSPSim还实现了常用的程序调试功能,包括反汇编,断点(breakpoint)及内存读写监视点(watchpoint)的设置,单步进入/单步跳过运行,符号信息与行号信息的查询,存储器与寄存器内容的查看与修改,函数最大和最小十个执行时间统计,函数执行次数统计,覆盖率信息统计,保存/加载当前存储器状态。

ADSPSim还以动态链接库形式提供,大量接口函数提高了系统的可操作性和可扩展性。

3.2 ADSPSim的构架

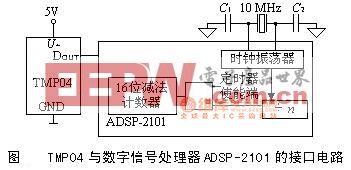

ADSPSim按照图1所示各功能单元抽象得出相应模块,如图2所示。

图2 ADSPSim功能模块图

前面提到过,运行于ADSP-2106x上的目标可执行程序为ELF格式。GNU的BFD(Binary File Description,二进制文件描述)链接库并不能支持AD公司所用的ELF格式,因此ADSPSim设计时未使用该链接库,而是单独开发解析模块,即程序加载模块。为了方便向其它格式扩展,利用类和继承的优势,创建程序加载器基类,实际各类文件格式的解析由派生类完成。程序加载模块不仅解析程序得到相应的符号表、行号信息给调试功能模块,还负责映射指令和数据至仿真的存储器。

寄存器模块实现了通用寄存器和IOP寄存器,相应详细的寄存器编码和格式见附录AC。为了方便调试程序,寄存器的内容可以通过接口函数显示修改。

仿真存储器内容由程序加载模块映射,各类芯片的存储器空间大小和编址不尽相同,但均分为内部存储空间、多处理器存储空间和外部空间3部分,其中的内部存储空间都包含IOP寄存器空间,正常字空间和短字空间。短字空间与正常字空间实际上是相同的物理空间,只是寻址方式不同,短字空间对内存以16bit为单位寻址,而正常字空间则以32/48位寻址。各芯片存储器不同之处详见第5章。注意,IOP寄存器实际上属于特殊的存储器空间。同样,存储器的内容也能通过接口函数显示修改。

调试功能模块提供对符号表、行号信息及其它调试信息的查询变量信息另外,ADSPSim还实现了调试运行功能,包括反汇编,单步进入/单步跳过运行,置断点/内存读写监视点,保存当前仿真器状态及存储器内容,或加载已保存的仿真器状态,统计函数执行时间和覆盖率信息等。

ADSPSim的关键模块为核心单元模块,即模拟了图1所示的核心处理器功能单元,包括包含有程序控制器,指令高速缓存,定时器及21kCore。程序控制器实现顺序执行、循环、子程序调用、跳转、中断等程序结构,及其它相关功能,详见第3章。21kCore包括了ALU、乘法器和移位器,并完成了三级流水中的译码和执行单元。图1所示的数据地址产生器(DAG)未单独实现,已合并至21kCore。核心单元部分各芯片也存在不同,例如中断基地址、短字空间地址的判断,这些细微的差别由相应的派生类实现。

图2中虚线框内为ADSPSim的功能模块,基于接口函数,图形界面模块提供用户对仿真器操作途径。

ADSP-2106x作为一个系列的数字信号处理器,其包含的四种产品指令系统和体系结构基本相同,唯一在于片上存储器的大小和外部接口不尽相同。仿真器基于面向对象的方法构架,面向对象技术的类和继承的利用,使得ADSP-2106x各产品的共性能很方便的抽象出来,相异之处由派生类实现,达到了代码的高度重用。

3.3 ADSPSim实现中的难点技术

3.3.1各类数据的表示

ADSP-2106x支持IEEE754/854标准定义的32位单精度浮点数,还支持相同格式的40位扩展精度浮点数(有额外的8位尾数)和16位短字浮点数(仅有4位指数12位尾数)。当然,ADSP-2106x也支持32位的定点格式,包括有符号或无符号的小数和整数(详见附录C)。ADSP-2106x数据寄存器为40位,用来存放上述定点和浮点数据。定点数据不难实现,而16/32/40位浮点数则需要额外构造浮点数据类型,来区分符号位、指数和尾数部分。运算时将构造的浮点数据结构转换为常见的浮点数进行运算,当然运算结果需要转换回来。

更特殊之处在于,ADSP-2106x的乘法单元包含80位乘法累加器MRF和MRB用于32位×32位=64位数据乘法。而C/C++中常用数据结构最多至64位,ADSPSim中构造了新的类作为80位数据以实现此类乘法(乘法具体算法见B.2.2C.5)。利用运算符重载使得该类能同常见的数据结构进行运算,同样也能对其进行赋值;另外为了在运算中判断是否上溢/下溢/为负,还提供了相应的接口函数。

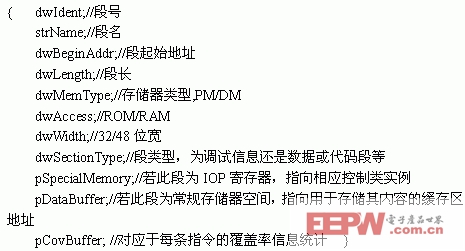

3.3.2存储器结构组织

程序加载模块解析目标可执行文件后得到的存储器内容,按段组织映射至虚拟存储器,段数据结构如下:

因为IOP寄存器实际上是特殊的存储器空间,因此单独由指针pSpecialMemory寻址其内容,而常规存储器空间则由pDataBuffer给定内容。覆盖率信息数组最高位表示是否覆盖,低两位:若为00表示顺序执行指令或者绝对跳转指令;01表示条件分支指令执行时条件不满足,未发生跳转;10表示条件分支指令执行时条件满足,发生跳转。

4 结束语

作为一种用以模拟可执行程序在目标芯片上运行情况的工具,ADSPSim已应用于型号工程,是进行嵌入式软件测试和计算机体系结构研究的有力工具,不仅可以单独的工具形式提供给用户用于测试,还能以动态链接库形式提供给软件仿真测试环境,是软件仿真测试环境的重要组成部分。

评论