DSP架构应对电网谐波污染分析的挑战

在过去,谐波分析仪不仅非常昂贵,而且难以集成到大规模制造的电表中。因此,对电网进行谐波污染分析是一件非常困难的事情,只能偶尔由专业操作员在某些特定位置进行。如今,芯片不仅可以集成更多的信号处理功能,而且尺寸更小、价格更低廉,能够实现对电网的高效使用和监控。

过去几十年来,电源系统呈指数式增长,其非线性特性引起了严重的谐波污染。这可能带来多方面的不利影响,例如:电气设备过热和过早老化,传输线路损耗增加,以及继电器保护失灵等。因此,业界越来越关注谐波污染问题,并采取了各项措施以实现更好的电网管理。其中,最佳的一个方法是在电网内设置更多的观测和分析点,并且延长监控时间。随着智能电表在全世界范围内的加快部署,满足上述要求的最佳器件会被用于其中。用于智能电表的ASIC集电能计量特性与谐波分析功能于一身,可能是最适合当下的理想解决方案。请切记,考虑到一块芯片内要嵌入大量DSP资源,同时又必须廉价、尺寸小、功耗低,可想而知频谱分析绝非易事。本文将讨论一种尝试满足所有这些需求的DSP架构解决方案。

基频估算和频谱成分提取

电网上不断变化的负载与相对恒定的发电输出之间存在一种动态的平衡关系,这导致在负载较高时,主电源频率会略微降低,而在负载较低时,主电源频率会略微提高。在电网高度发达并受到密切监控的国家,频率偏移量相当小,但在电网控制不佳的地区,频率偏移量可能大到足以影响电气设备。为此,业界已进行大量研究工作,试图找到通过优化各种参数,如精度、速度、噪声和谐波抗扰度等,来实现跟踪频率的最有效方法。

就电源系统的安全性、稳定性和效率而言,电网的频率是与电流和电压同等重要的工作参数。可靠的频率测量是有效的进行电源控制、负载减轻、负载恢复和系统保护的先决条件。

检测和估算频率的方法有许多种。例如,过零方法通过测量两个相继过零点之间的时间间隔来检测频率,这种方法的优点是非常容易实现,缺点是精度较低,并且易受谐波、噪声、直流成分等影响。基于DFT的算法可以利用采样序列来估算频率,但它对输入信号中的谐波非常敏感。针对本文所述的DSP架构,我们考察了一种基于数字PLL的方法,发现它很有效,具有高抗扰度,同时还能提供精确的频率估算。

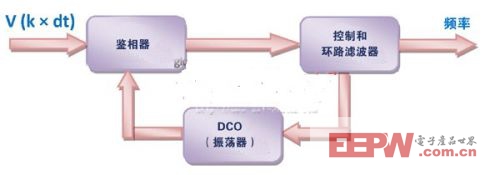

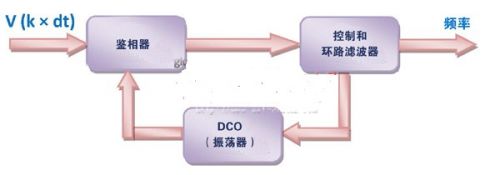

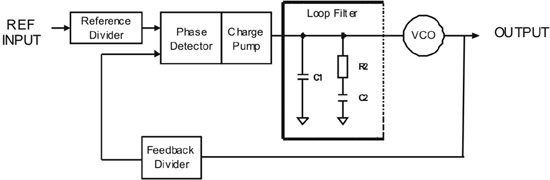

图1所示为标准数字PLL结构及其三个主要模块。相位误差检波器将输出发送到环路滤波器,环路滤波器进一步控制一个数字振荡器,目的是最大程度地降低相位误差。因此,最终可以获得输入信号基频的估算值。控制环路经过优化,在45 Hz到66 Hz的标准电网频率范围内可提供最佳的锁定参数性能。

图1. 基于数字PLL结构的频率估算

评论