ASIC和SoC设计中嵌入式存储器的优化

在传统的大规模ASIC和SoC设计中,芯片的物理空间大致可分为用于新的定制逻辑、用于可复用逻辑(第三方IP或传统的内部IP)和用于嵌入式存储三部分。

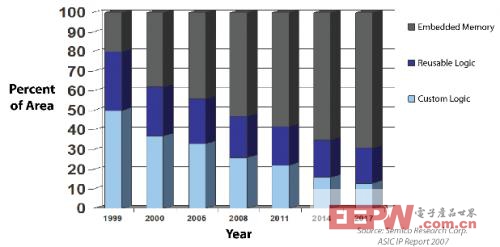

当各厂商为芯片产品的市场差异化(用于802.11n的无线DSP+RF、蓝牙和其他新兴无线标准)而继续开发各自独有的自定义模块,第三方IP(USB核、以太网核以及CPU/微控制器核)占用的芯片空间几乎一成未变时,嵌入式存储器所占比例却显著上升(参见图1)。

图1:当前的ASIC和SoC设计中,嵌入式存储器在总可用芯片空间中所占比例逐渐升高。

Semico Research 2013年发布的数据显示,大多数SoC和ASIC设计中,各式嵌入式存储器占用的芯片空间已超过50%.此外,许多大规模SoC嵌入式存储器的使用目的和主要性能也各不相同,如图2所示。

图2:多核SoC的各种嵌入式存储器IP.

由于可以根据设计目的,通过采用正确的SoC存储器类型来优化设计,因此,对于设计师来说,利用各种存储器IP具有非常重要的意义。设计师可通过恰当分配各种存储器IP所占比例,实现速度、功耗、空间(密度)以及非易失性等各种性能参数的优化。

嵌入式存储器的主要设计标准

各种应用设计中,最佳存储器IP的确定主要基于以下5个驱动因素,如图3所示:

1功率

2速度

3可靠性/良率

4密度

5成本

图3:确定存储器IP的主要因素。

通过对上述各性能决定要素进行权衡,可得到最优解决方案。许多情况下,存储器编译器可根据输入存储器设计生成流程中的各种驱动因素,自动生成性能经过优化的特定存储器IP.同样重要的是,存储器IP的支持性结构应适用可靠的验证方法,且生成的IP良率最高。最后,为实现产量与质量的最优化,存储器编译器还应直接生成GDSII,无需人工干预或调整。其他要素还包括良好的设计余量控制、对自动测试图形向量生成和内建自测试(BIST)的支持。此外,最好具备通过BIST的单步执行进行硅片调试的功能。

评论