基于LVDS的高速图像数据存储器的设计与实现

采集数据的有效传输和存储转发技术的发展保证了数字图像在现实中广泛应用。如今,从多媒体通信领域的远程教育、图像监视到医学上的远程会诊,都和数据的有效传输及存储转发技术息息相关。在国防工业领域,图像数据的采集存储和连续有效转发也起着巨大的作用,航空遥感图像和卫星遥感图像的处理加工,电视制导中数据视频图像的传输,都离不开图像传输存储技术。本文设计的基于Flash的高速大容量固态数据存储器,采用了基于LVDS的数据传输方式传输两路高速图像数据,实现图像数据的高速实时存储。不仅具有处理速度快、设计灵活性高等特点,还具有可配置性和可重构性的特点。

1系统总体设计

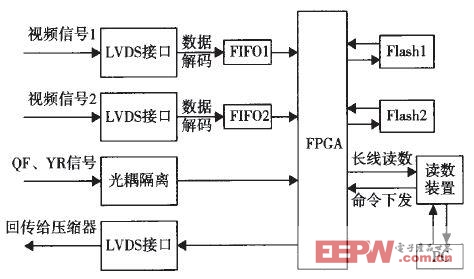

本文介绍的图像存储器在飞行任务中负责完成两路独立视频信号的采集存储任务。视频图像存储的总体结构框图如图1所示,当光耦接收到起飞和诱饵两个控制点火信号后,FPGA就控制视频信号1、视频信号2经2路独立的LVDS接口传输,并分别解码后缓存到2个外部FIFO中,最后写入到2个各自的存储模块Flash当中。在系统工作时,读书装置可以实时监测记录器关键状态参数;系统存储工作完成后,读数装置通过LVDS接口以20 Mbyte/s的速度远程高速读取图像记录器的数据,将数据回传至上位机进行存盘判读。

图1存储器功能框图

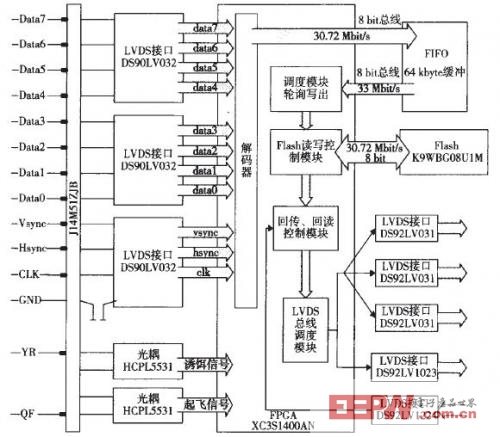

本设计存储器负责接收的2路图像尺寸均为640 X480 byte,在飞行器内部传感器下发起飞和诱饵两个关键信号的控制下,图像数据存储器分别对这2路视频图像信号进行采集,采样位数:8 byte/像素,输入数据码率:30.72 Mbyte/s,帧率:100 f/s(帧/秒),然后将解码后的数据分别存储到2个Flash中,最后准确地完成数据的转发任务,使图像数据顺利进入下一模块。存储器视频信号处理硬件电路框图如图2所示。

图2存储器视频信号处理硬件电路框图

2硬件电路设计

2.1 LVDS长线传输电路设计

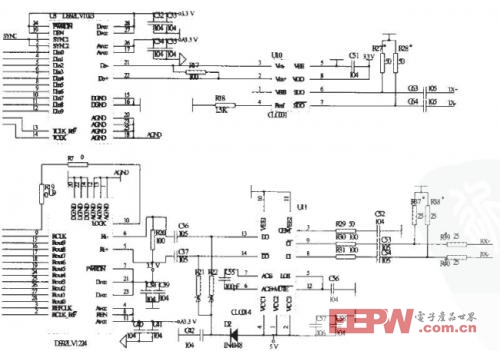

本设计系统中摄像头发出的视频图像信号属于高速变化的信号,容易受到噪声影响。低压差分(Low Volt-age Differential Signaling,LVDS)数据传输技术是一种新型的、具有很低的差分电压摆动幅度的信号传输方式。LVDS传输过程中以差分的方式传送数据,从而具有很低的串扰和噪声以及只消耗很少的功率。此外它通过一对并行PCB走线或平衡电缆传输数据,可以达到100 Mbit/s甚至高于1 Gbit/s的高速率数据传输。解决了高速数据的有效传输,同时也将有助于降低系统设计复杂度,提高系统可靠性。基于LVDS技术的传输特点及应用优势,本设计中图像输入接口采用LVDS进行图像数据接收。设计中为满足信号实时高准确性的传输,在LVDS发送端采用串化器和驱动器相结合的方式增强信号;在LVDS接收端采用均衡器和解串器相结合的方式,来补偿信号长线传输过程中的损耗。这样高速图像信号可以稳定地传输上百米。如图3为LVDS接口端硬件电路设计图。

图3 LVDS接口端硬件电路设计图(点击查看大图)

2.2 FIFO的电路设计

本设计中进入FIFO前经解码得到的图像数据传输速率为30.72 Mbit/s,因此在FIFO的选型中,必须选择一款读写速度快而且容量大的外部FIFO来缓存图像数据。经过计算并对比分析后,本设计选用了CYPRESS公司生产的64 kbit x 18 bit的CY7CA285V:

1)CY7C4285V拥有66.7 MHz的最大工作频率,10 ns的最小读写周期,完全可以稳定、可靠地接收码率为30.72 Mbit/s的图像数据,也满足25 ns读写周期的要求。

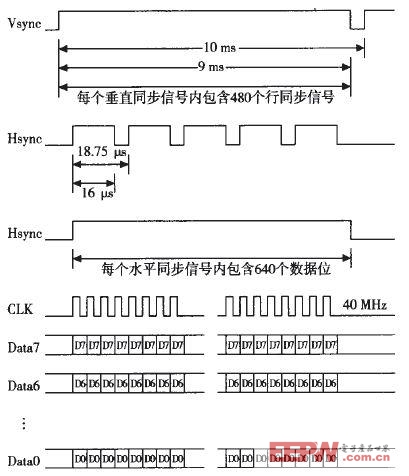

图4单路图像数据接收接口时序定义图

2)从FIFO接收图像数据的时序图中(如图4)可以看出,一个水平同步时间内,写入FIFO的图像数据有640 byte,而读出FIFO的数据量为33 Mbyte/s x 18.75μs=618.75 byte.这样每一个水平同步时间内FIFO中就会剩余640 byte-618.75 byte=21.25 byte的图像数据。当垂直同步信号拉低时,FIFO中剩余的图像数据量达到最大,本设计FPGA控制FIFO半满即读,那么FIFO的容量至少应为:2 x 21.25 x480=20400 byte.显然容量为64 kbyte的CY7C4285V可以满足设计要求。

存储器相关文章:存储器原理

评论