嵌入式MCU硬件设计概述

(6)存储器管理方案设计

存储器是MCU中占面积较大的模块。一个MCU中可能同时含有ROM、SRAM和FLASH三种存储器:ROM用于放置Boot Loader、IP Drivers等,SRAM用于提高软件运行速度、存放临时数据,FLASH用于存放应用程序和数据。由于FLASH的读写速度比较慢,为了提高FLASH的读写速度,可以采用预取缓冲器和写缓冲器来加速指令和数据的缓冲。由于各个存储器都有自己的地址空间,因此很方便用户访问。为了便于系统管理,通常设计一个存储器管理模块,并在系统控制模块中设计对应的控制寄存器。

(7)在线调试方案设计

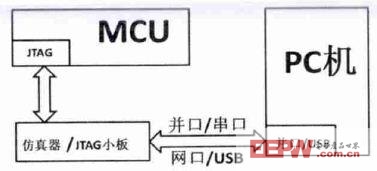

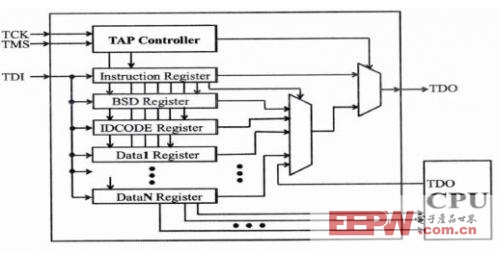

目前,比较常用的在线调试方式为串行调试,如JTAG、EJTAG、UART等,使用PC机的并口、串口、网口或是USB接口,使得在线调试简单方便,成本低廉,如图2所示。由于被调试的程序要在目标板上运行,而且MCU必须正常工作,因此需要设计一个专用的调试模块以保证上位机软件可以调用CPU来进行软硬件的在线调试,并且符合IEEE1149.1的协议标准,此模块的基本结构如图3所示。

图2典型在线调试系统示意图

图3调试结构示意图

(8)测试方案设计

MCU的测试方案主要包括物理测试、功能测试和性能测试几部分内容。先要根据时钟方案和复位方案对MCU进行时钟测试,确保时钟电路工作正常;再对CPU进行功能测试,因为CPU是MCU的控制核心,只有CPU正确运行才能对其他IP核进行测试;然后再依据设计规格书对MCU外围的数字IP核和模拟IP核进行功能测试和性能测试。

5.2系统级验证

为了确保设计的正确性,流片之前必须对MCU进行全功能验证。因此需要使用多种IIP和VIP来搭建一个系统级验证平台,依据设计规格书制定详细的验证方案,通过仿真工具,采用定向和随机的方式或采用比较流行的OVM、VMM和UVM等验证方法学、逐个IP核来验证MCU的全部功能是正确的,重点是系统控制单元、总线仲裁器、功耗管理等为系统功能定制设计的非标准模块。

5.3 FPGA原型验证

由于系统级验证使用的是EDA工具进行软件仿真,仿真的速度比较慢,因此可以通过FPGA原型验证的方式来加速系统级验证的速度,尤其是需要将那些功能比较复杂、规模比较大的模块下载到FPGA中,而且应尽可能使用规模比较大的FPGA,如Virtex-7系列、ArriaV系列等。搭建FPGA验证平台时,不仅可以使用一块FPGA,也可以使用多块FPGA,最好能够将设计的所有模块全部下载到FPGA中。FPGA原型验证不仅要验证硬件的正确性,还要验证IP核驱动程序的正确性,同时也可以验证目标应用程序的正确性。

5.4物理设计

在对MCU系统级验证和FPGA原型验证后,需要进行物理设计:依据设计规格书制定合理设计约束,从逻辑综合到自动布局布线,再到物理验证、形式验证、静态时序分析和功能验证,完成从RTL到GDSII的转换过程,最后将数据发送至代工厂进行加工制造。

5.5文档设计

文档是MCU设计过程中很重要而且很必要的环节,且应该在设计的不同阶段,以模板的形式规定在此阶段所要完成的文档设计,并由项目负责人进行详细审查,从而确保一旦设计中出现了任何问题,都可以查找相关的设计文件以及对应的设计文档,尤其是设计的细节需要体现的很完整。

6结束语

以上只是简要概述了MCU硬件设计的主要方面。若要设计一个性价比高、竞争力强的MCU,还需要进行大量的、详细的工作,尤其是电路的全功能验证和详尽测试,并搭建一个MCU平台来进行系列产品的开发,以保证产品可以源源不断地进入嵌入式市场。

评论