模拟与数字的智能集成解决棘手的嵌入式系统问题

高速逐次逼近型寄存器(SAR) ADC非常适合这种应用,因为,此类ADC拥有适当的精度(13 ENOB),其超快的转换速率可支持较高频率的控制环路,能对多个输入通道进行多路复用,还具有低延迟( 1μS)的特性。该系统有两个ADC,用于对电网电流和电压进行同步采样。需要大量输入通道来连接ADC,以便对系统中的多个点进行监控——有时最多需要24个通道。为满足该要求,我们设计了带缓冲功能的特殊多路复用通道,并与ADC接口。

为了支持多级转换和高速控制环路,需要选择架构性能适当且具备高速运行能力的处理器内核。在本例中,设计温度范围运行速率大于200 MHz的ARM Cortex-M4即可满足该需求。

正弦滤波器(如图2所示)与隔离式ADC结合使用。这样可对电网中的电流以及直流注入进行测量,以防止变压器饱和。传统方法是用一个霍尔效应电流传感器,但与隔离式ADC相比,这种方法成本较高。该方法假定,正弦滤波器集成于混合信号控制处理器之中,从而消除了物料清单中表现为可编程逻辑的额外芯片的必要性。另外,相对于霍尔效应传感器,ADC正弦滤波器组合的隔离还具有线性度更佳的额外优势,有利于减少谐波失真。

随着电网智能化步伐的加快,太阳能光伏逆变器将需要具备更多智能,以帮助解决电网不平衡问题。这是指来自多个源的电力超过需求的情况。为此,业界十分重视光伏系统智能,以电网整合为目标,电网的每个供电商必须相互合作以实现电网的稳定。电网整合要求更好地对馈入电网的电能进行测量、控制和质量分析。一种专门为电网电力质量监控而设计的谐波分析引擎有助于满足该需求。通过计算几个变量(包括谐波失真、功率、rms电压、rms电流、VAR、VA和功率系数,可以实现对电力质量的监控。用于执行这些计算的专用引擎不但可以带来超高的精度,同时还能减轻ARM Cortex-M4内核的负担,使其无需执行该任务。

利用在设计时充分考虑了这种最终应用的混合信号控制处理器,太阳能逆变器可以在系统层面获得极大的优势。基于对市场趋势的了解以及坚实的系统知识,可以打造出智能化集成芯片,这种芯片不但能支持新一代拓扑结构,减少芯片数量,同时还能带来更多功能以支持与智能电网的接口。

在关于发电方式的环保担忧之外,人们还十分关心能源的使用效率问题。鉴于电机占全球用电量的40%,所以问题是如何提高这些系统的环保性。答案在于提高其效率,由此减少能耗。通过普及高效电机而节省的能源量十分可观:每年可节省数千亿千瓦时的用电量,可减少大气中二氧化碳排放量数百万吨。显然,高效电机的影响具有十分重要的意义。

具体地,有多个关键因素推动着高效电机的应用。其中一个是环保问题推动的政府立法。欧盟已经实施相应的法规,将来还会实施更多法规,强制要求使用更高效的电机系统。另一个关键推动因素是全寿命成本优势。在电机控制系统的成本中,材料约占15%,运行所用能源成本占85%.可见,通过提高效率,降低电机系统全寿命成本的潜力是非常巨大的。

提高效率的方式包括特别的电机设计,电机类型的选择,为不具备这种控制的系统添加可调速驱动器(ASD),以及针对效率而优化的控制算法。就特别的电机设计和特定电机类型的选择而言,永磁电机一直是关注重点,其使用呈增长之势。永磁电机的效率最高可达96%,超过了欧洲超高效能效标准(IE3)。

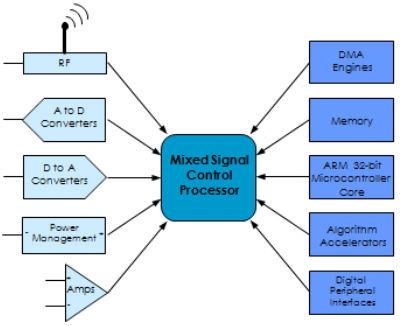

智能集成式混合信号控制处理器有可能实现ASD和控制算法的改进。以成本优势明显的方式集成基于ARM的CPU子系统、PWM、ADC和多路复用功能,结果可以在系统层省去ASD的物料成本。

利用转换时间较快的高精度ADC,可以改进控制算法。结果可增进电机系统的总体效率。精度高于12位的ADC可提高精度,用其来控制相位电流。然而,不能用采样转换延迟控制来换取更高的精度。这样就不能选择通过均值或过采样方式提升SNR的ADC.需要以终端机器(比如,贴片机)

的运动速率来测量变量。快速转换时间,加上快速ARM微控制器内核,可以加快控制环路的运行速率,改进响应时间,缩短建立时间。反过来,这又能提高生产线系统的吞吐量和效率,从而降低生产成本。

就如太阳能光伏应用一样,SAR ADC是电机控制的良好选择。在电机控制的例子中,可以设计出高性能SAR ADC,无需均值或过采样也可达到要求。

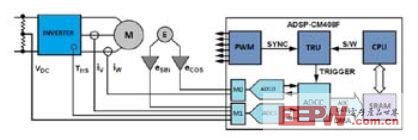

图3中的各种知识产权模块都经过精心设计,相互配合良好。需要的结果是一种高度敏捷的仪器仪表子系统,可以采集多个计划精确的采样,并高效地将其交付给ARM的主存储器。对于电机控制,相位绕组电流和其他测量值均可在PWM周期中的精确指定点进行同步采样。在此基础上,采样数据可以在不产生开销的情况下高效地移至微控制器的存储器以进行处理。为了实现这一目标,混合信号控制处理器中有5个不同的模块需要协同工作。

图3.电机控制系统功能框图

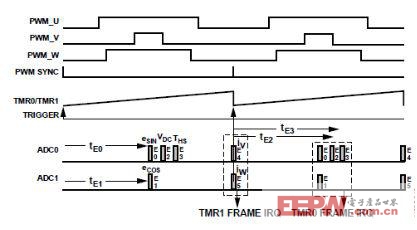

周期开始时,发送一个PWM脉冲到触发路由单元(TRU),后者负责将触发主机连接至触发从机。在本例中,PWM为触发主机,ADC控制器(ADCC)定时器为触发从机。ADCC需要具备管理大量事件的能力,并使用定时器(TMR0/TMR1)来跟踪从PWM触发到启动特定ADC事件所需时间。在定时器与特定事件相匹配的情况下,选择的是ADC输入多路复用(M0和M1)和通道(ADC0和ADC1)。接下来,将转换开始信号发送至ADC.采样数据从ADC移至ADCC,然后从ADCC通过DMA移至微控制器SRAM.

下面的图4所示为PWM脉冲、PWM同步和ADCC所控制ADC事件之间的相对时序。

图4.用ADC对5个不同电机控制变量进行采样的时序

对于面向电机控制的混合信号控制处理器设计,其在PWM、TRU、多路复用、缓冲、SAR ADC和DMA

方面有着良好的知识产权基础。然而,为了在PWM周期中实现ADC采样的精密时序,必须对这些模块的设计进行特别的改动。ADCC模块的必要性是有事实依据的,即其他知识产权模块集成于单枚芯片中,它们之间需要协调。ADCC即专门针对这一要求而设计,充分发挥了两个ADC引擎的高速优势,这些ADC引擎的转换时间快达380 ns.

评论