基于CPLD的CCD Sensor驱动电路设计

0 引 言

本文引用地址:http://www.amcfsurvey.com/article/255996.htm视觉信息是客观世界中非常丰富,非常重要的部分。随着多媒体系统的发展,图像传感器应用越来越广泛。不仅用于摄录像机,安保产品、数码相机及计算机镜头等,而且开始用于传统上的非视像产品,如移动电话、个人数字助理(PDA)等。传送优良的图像,兼顾体积小、重量轻、噪声低、速度快等优点,CCD图像传感器是一个不错的选择。

CCD(电荷耦合器件)作为一种光电转换器件,应用的关键技术是产生正确的驱动器信号和相应的控制信号。不同型号的CCD,驱动信号时序千差万别:有高速CCD驱动,高帧率CCD驱动,高分辨率CCD驱动,紫外CCD驱动,其中既有线阵型也有面阵型。传统的驱动器都采用标准的TTL数字集成电路、单片机或者EPROM器件等,这种电路体积大、电路复杂、成本较高并且工作速度慢。在此提出使用可编程逻辑器件(PLD),完成CCD驱动,较好地解决了这些问题。

1 ICX285AL时序分析

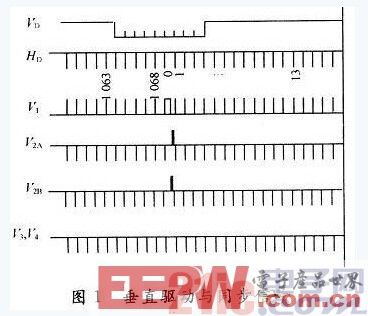

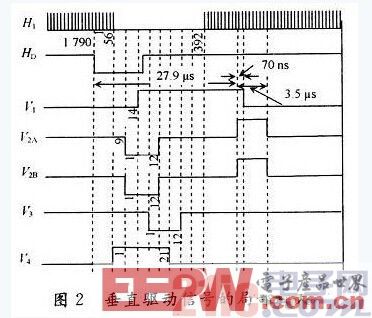

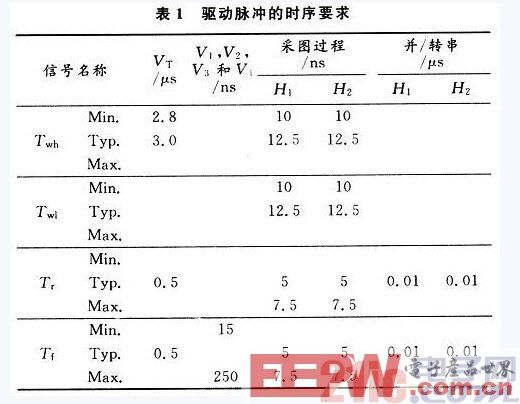

ICX285AL是Sony公司的一款行间转移、方像素、固态面阵图像传感器,其的总像素是1 434×1 050,有效像素是1 392×1 040,活跃像素是1 360×1 024。垂直寄存器有5个驱动时钟V1,V2A,V2B,V3,V4。水平寄存器有4个驱动时钟,2组H1,H2。图1表明水平同步信号HD、垂直同步信号VD、垂直驱动信号的时序关系。图2为上述信号的局部放大的相位关系。驱动脉冲的时序要求如表1所示。

注:VT:读出时钟信号(Readout clock);Twh:脉冲商电平保持时间;Tw1:脉冲低电平保持时间;Tr:脉冲上升沿时间;Tf:脉冲下降沿时间。

2 ICX285AL驱动逻辑设计

ICX285AL驱动电路主要有三部分:水平和垂直同步信号,刷新信号和四相位驱动脉冲。

2.1 水平同步信号HD和垂直同步信号VD

由ICX285AL原理可知,基本时钟CLK循环周期应当设为1 790。水平驱动信号H1,H2和垂直驱动信号V1,V2A,V2B,V3,V4,以及转移信号SUB在此基础上建立相互的时序关系。H1与H2相位相差180°,V2A与V2B相位完全相同。

设置水平同步信号HD和垂直同步信号VD的关系,可定位sensor有效行的起始位置以及用于校正目的的暗像素(dark pixel)位置。如图3所示,通过sensor采集的图像有效行数为1 063-3=1 060。图4表明水平驱动信号H1与水平同步信号HD的时序关系。水平驱动信号H1、H2,水平同步信号HD与基本时钟信号clk之间的时序关系如图5所示,完全满足HD的相位要求。

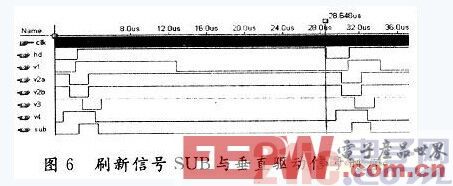

2.2 刷新信号SUB

刷新信号SUB表示Sensor每传输一行图像信号,就会有一个刷新脉冲产生。参照ICX285AL原理,系统的基本计数器Counter计数范围从1~161之间的值时,SUB为“0”,低电平;Counter计数范围从161~287之间的值时,SUB为“1”,高电平;当为其他值时,SUB为“0”。图6为刷新信号SUB与垂直驱动信号时序关系的仿真结果。

2.3 四相位驱动脉冲

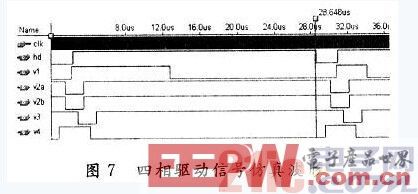

根据四相CCD电荷转移的原理,CCD中的电荷根据四相时钟信号驱动,实现电荷转移。设计过程中必须保证四相驱动信号V1,V2,V3,V4的时序关系。图7所示为四相驱动信号与水平同步信号的仿真波形。

3 驱动电路CPLD实现

采用Altera公司的CPLD芯片EPM3256AQC208完成CCD驱动电路,方案已应用于工业摄像头系统。利用泰克500 MHz示波器实测波形如图8所示,图9为水平驱动和垂直驱动信号局部放大波形。时序及时延参数均满足要求,工作稳定可靠。基于PLD技术的方案,易于实现与其他芯片的接口,具有高度灵活性、天然的并行性和快速成型等特点,同时可通过编译平台方便设置PLD芯片的驱动电流,有效降低系统噪声,是一种性价比较高的选择。

评论