利用普通数字存储示波器排除嵌入式系统数字类故障

虽然目前的服务器和PC越来越青睐先进高速处理器,但是低档的20或30MHz处理器在现实生活中还在发挥作用。尽管这些粗笨的微处理器设计陈旧,已有多年历史,它们却依然在机械、消费类电子及车用电器中占有一席之地。

这些嵌入式处理器及其应用有什么共同点呢?归纳起来有这样几个明显特征:第一,这类处理器经过很多产品充分验证,人们都非常了解,而且开发可得到广泛支持,易于设计;第二,与现有高端方案比较,其时钟速率相对较慢,总线速率也很慢;第三,应用系统(从自动售饮料机到航空电子设备)必须要有很高的可靠性;最后,成本(包括设计、制造和维护费用)必须尽可能低。

还有一个特性值得注意,即目前存在这样一个稳定的发展趋势,这些嵌入式器件和总线时钟速率都在不断提高,倒不是说要赶上速度最快的服务器,而是将朝“短时钟周期”器件方向发展,时钟速率比以前快5~6倍。和过去的处理器相比,新器件具有相同引脚和功能,但能在给定时间内做更多工作,它可执行更多指令周期完成更复杂工作而不会拖慢整个系统运行速度。这一点尤其对软件开发商有利,因为耗时的代码优化不再显得重要,新产品将会更快更便宜地推向市场。

进行基本数字检查的普通示波器带宽已比以前翻了一番,达到200MHz,而且一些非常有用的“高档”测量特性如高级触发、快速傅立叶变换(FFT)分析及彩色显示等也都相继加入到低档仪器中。如今的设计人员在面对民用产品嵌入式处理器时,也都能用得上数字式故障检测方案。

带宽决定应用

不久前生产的处理器和十年前生产的同一器件相比,多了一个隐蔽的“性能”,即信号边缘转换速度更快。从15年前生产这些产品所使用的CMOS工艺到5年前开发的快速5V工艺,边缘转换速度提高了约3倍,很多新设计都用这种最快的5V工艺,甚至有的还进一步降低内核部分电压而只在外围采用5V,对后者而言还能达到更快时钟速率,这种速度加快是硅片特征尺寸缩小所带来的副产品。

边缘速度更快通常是件好事,可减少系统内的时延、设置时间及冲突等问题,但传播延迟更短(大部分是由于CMOS更快边缘速率所造成)也会产生不利影响。当这类延迟越来越短时,通常取决于地址线逻辑和总线控制线间延迟的地址解码余量将遇到更多麻烦。因此设计人员需要知道并了解这些边缘状况、越来越窄的瞬时现象及高速转换时可能出现的其它脉冲特性。

在为一个含20MHz嵌入式处理器的数字设计选择DSO时,人们可能会认为用带宽50MHz或100MHz仪器对付这项工作完全绰绰有余。当然对一些基本故障检测,诸如有没有信号或者时序和同步是否准确之类的问题,确实是这样的,但其它细节可能就不那么明显。

具有较高带宽的DSO比低带宽仪器能更加深入地了解信号特性,因为示波器上升时间已成为确定被观察信号质量的因素之一,有公式如下:

测得上升时间=√(示波器上升时间)2+(信号上升时间)2

在低带宽观察时显得“正确”的脉冲可能会在前沿有一个幅值偏差,使其表现像两个脉冲;或者总线输出上的一个很窄瞬时信号可能完全注意不到,导致后面器件输入不稳定。如上面公式所示,一个200MHz的DSO可以捕捉到100MHz仪器看不到的细节。

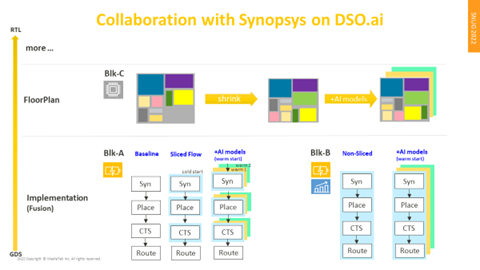

DSO带宽大的好处不仅仅限于观察信号边缘,使用高带宽仪器时,接地反弹、噪声、串扰及其它许多偏差都更易于观察到,也更不容易忽略。带宽越高,信号再现就越准确。图1显示了同一信号在60MHz和200MHz带宽示波器上看到的不同情形。

用条件触发检测时序问题

在数字存储示波器中,触发条件选择是一个重要但有时却不太为人所知的省力工具,它使DSO触发符合所指定的条件。如同显示波形一样,条件触发是嵌入式系统检测的一个基本工具,很多人使用噪声抑制(通常增大触发滞后)来限制短脉冲,并用各种带宽限制选择所需要的信号。

评论