使用NI PXI矢量信号收发仪进行802.11ac测试

挑战

在无线标准越来越多元,且设备复杂度与日俱增的同时,必须降低无线区域网络(WLAN)的测试成本,保有高的测试精准度,并且缩短特性测试时间。

解决方案

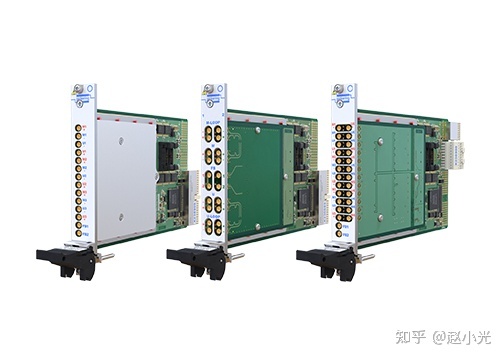

使用NI PXI构架的矢量信号收发仪与NI LabVIEW FPGA模块,构建灵活的自定义WLAN测试系统,相比以前的堆叠式仪器,可缩短200倍的测试时间,进一步减少成本,并提升设备特性。

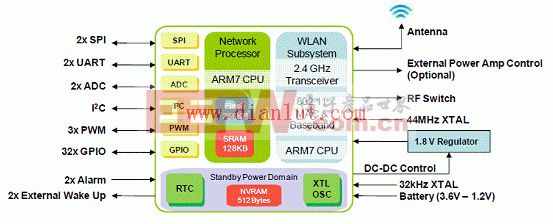

过去20几年以來,Qualcomm Atheros公司在网络连接、消费性电子、运算和移动设备通信的新一代无线技术领域中一直处于领导者的地位。 现在我们正对WiFi等高传输率的无线技术进行改革,以便满足新的连线应用需求。 最新的Qualcomm Atheros芯片是一种具有3组无线电的多重输入/多重输出(MIMO)收发器,适用于最新的WiFi标准802.11ac。

新型WLAN测试系统的需求

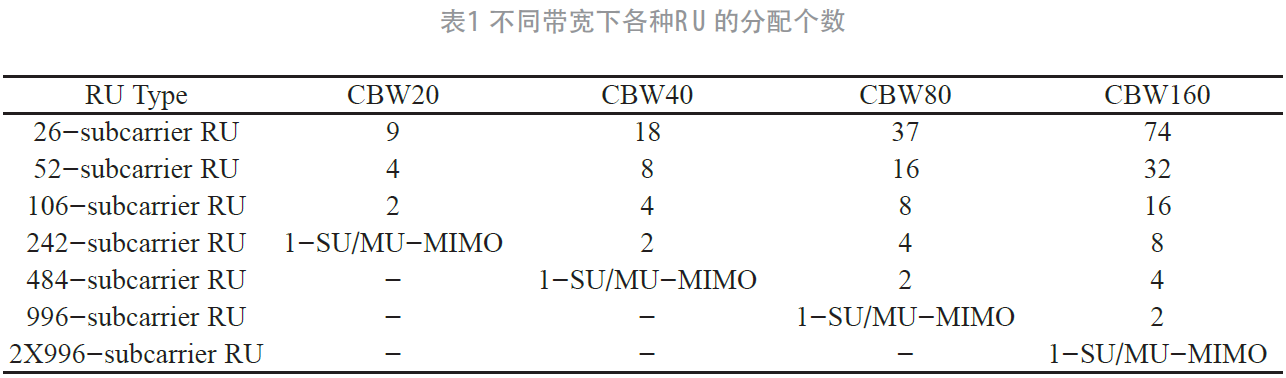

由于无线标准越来越复杂,这些设备的运作模式数量也会随之飙升。 我们会逐渐改用最新的WiFi标准,802.11ac ,所以要持续增加新的调制方案,以及更多的通道、频宽设定与额外的空间串流数目。 此外,数以千计的独立运作增益设定也会让WLAN收发器的特性测试变得更加棘手。

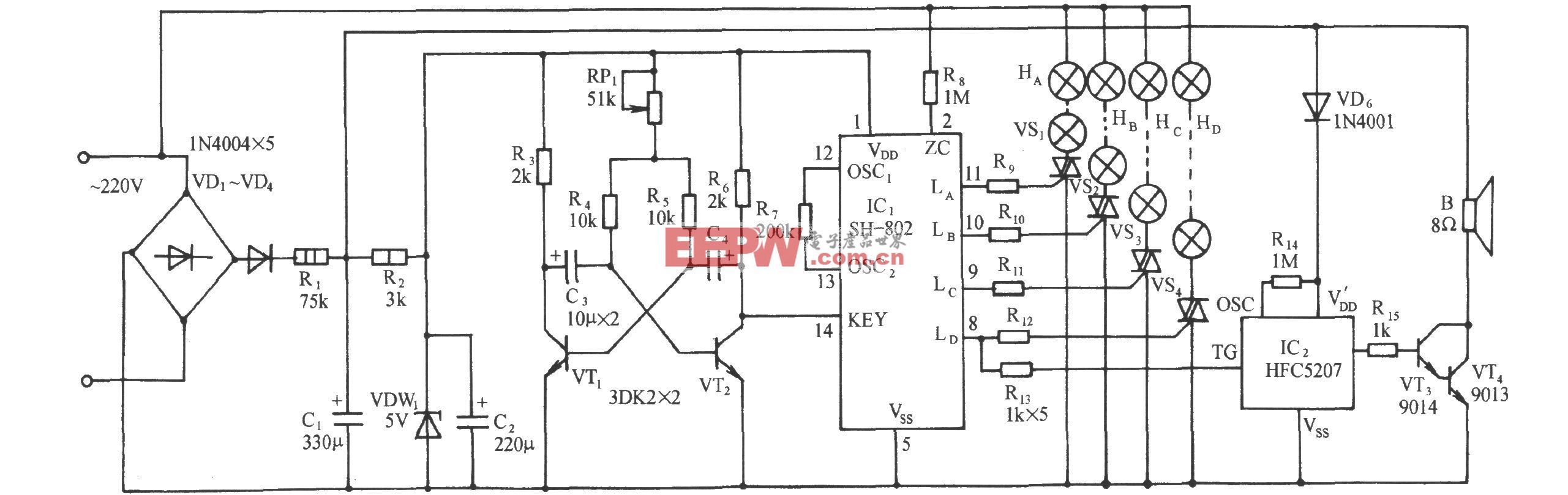

WLAN收发器的每个组件都具备多重增益阶段。 为了在低成本的CMOS流程中开发出高性能无线电,Qualcomm Atheros的设计团队必须针对每个无线电阶段采用灵活的操作方式。 一旦加入新的构架阶段,多重增益设定便会大幅提高可能的设定组合数量,因此单一运作模式便可能具有成千上万个数据点, 而且这只是一个无线电收发器的数据点而已;如果系统搭载多个天线的话,MIMO设定的电路排列数量也会持续增加。 随着可能的设定组合数量激增,要避免测试时间延长便会是相当困难的挑战。

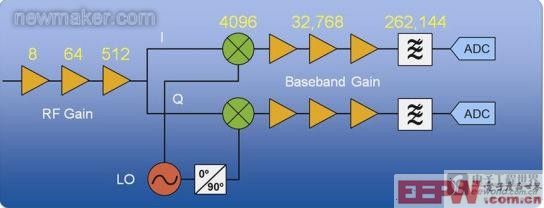

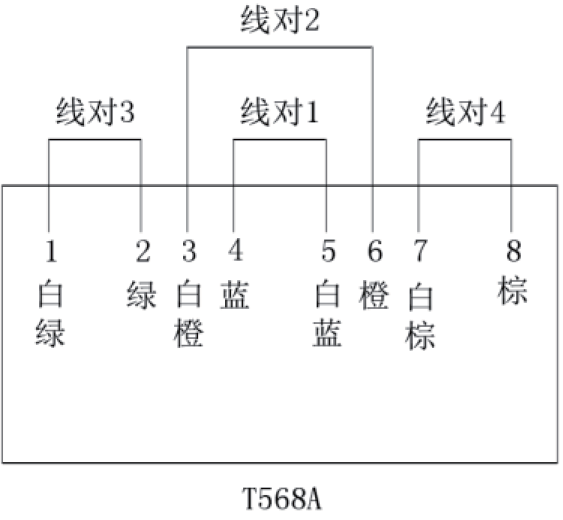

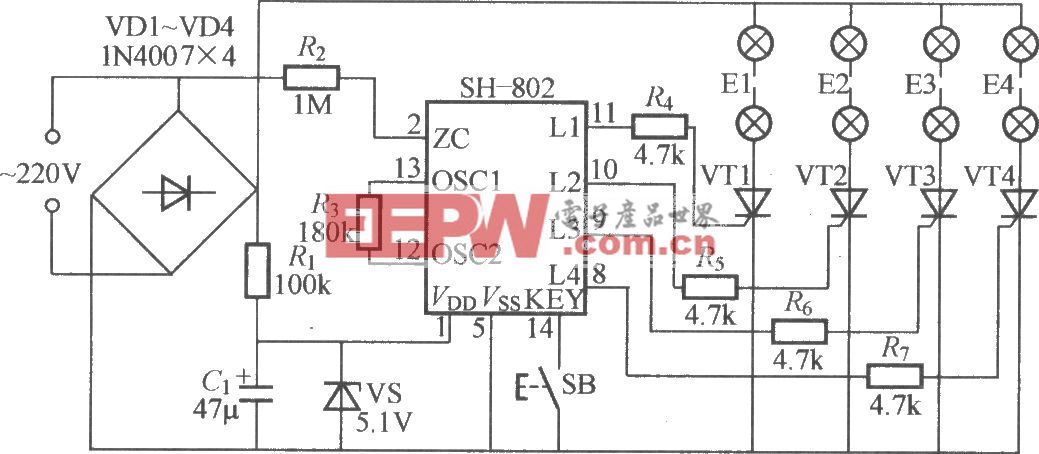

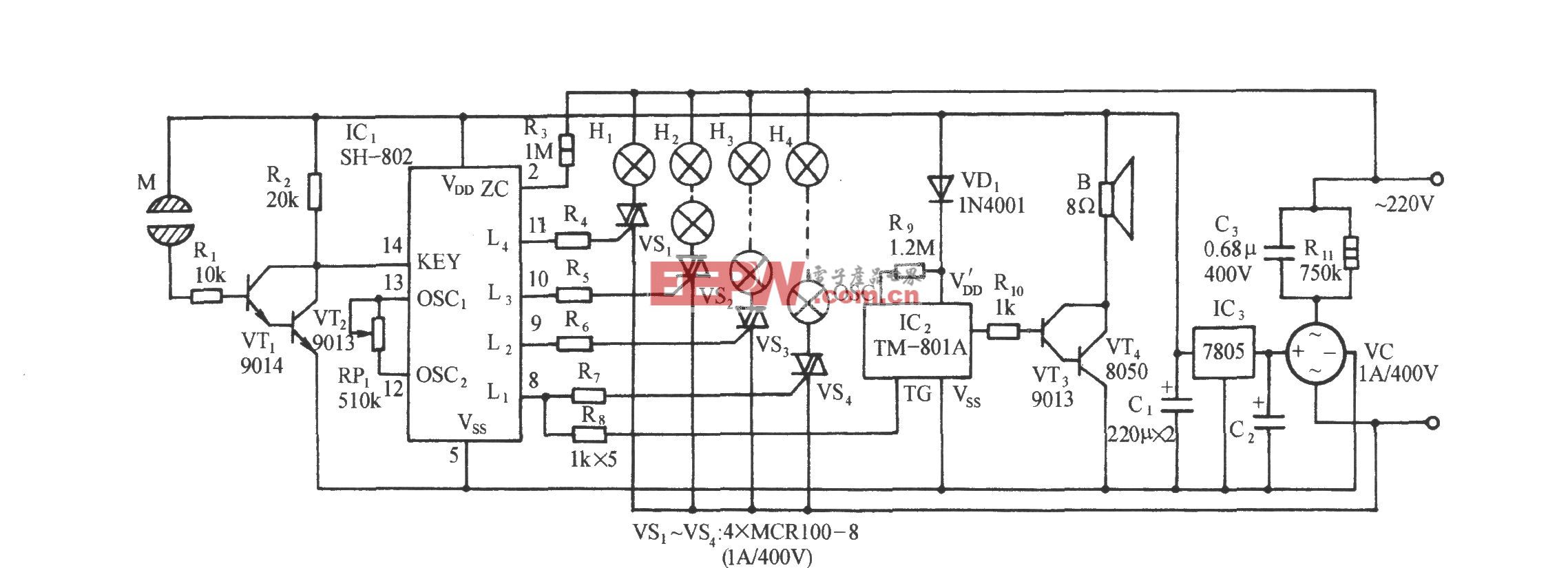

图1. 以常见的WLAN接收器程序框图为例,可以看出每个组件都具有多重增益阶段,

因此一个接收器可能会有成千上万种不同的增益设定

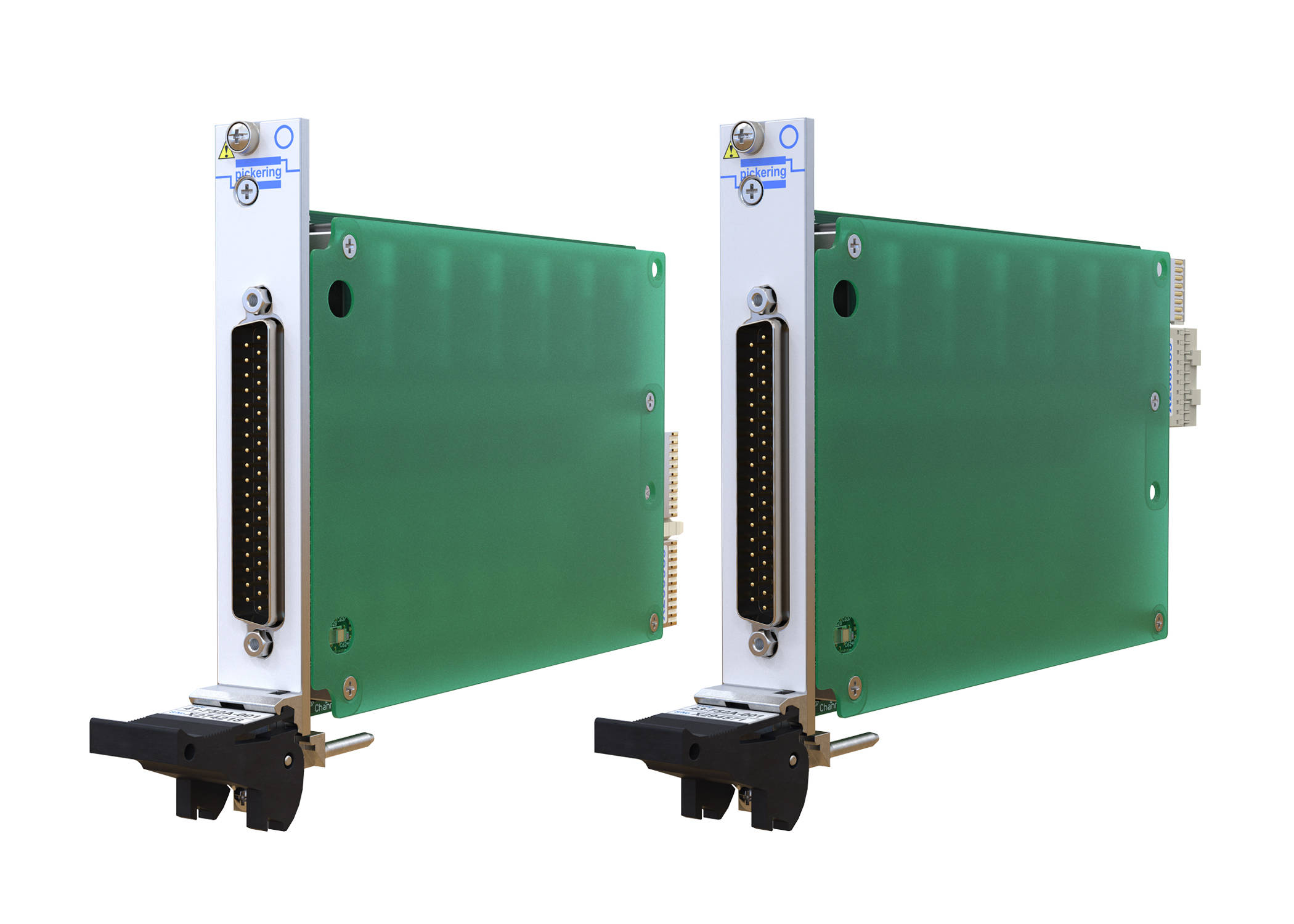

为了解决这类测试时间的挑战,Qualcomm Atheros采用了NI PXIe-5644R矢量信号收发仪。 由于NI PXIe-5644R内建FPGA,所以可通过矢量信号收发器内的射频信号发生器/分析器,同时控制芯片的数字界面。

一般而言,FPGA的程序设计必须通过VHSIC硬件描述语言或Verilog。 但许多工程师和科学家并不熟悉这些复杂的语言,或是需要特定的工具,才能针对高阶抽象层提高设计产能,进而简化FPGA代码的生成流程。 由于LabVIEW能够清楚地表现并行架构和数据流,非常适用于FPGA程序的编写,所以用户不论有没有传统FPGA设计的经验都能高效运用可重新配置硬件的功能。

Qualcomm Atheros采用LabVIEW来设计NI矢量信号收发器的FPGA,以便控制待测设备并处理数据。 仪器内部即可执行处理程序,无需通过总线来回传输至控制器,因此有助于大幅提升测试速度。

评论