基于ARM+FPGA的高速数据采集智能控制器设计

摘要:文章以嵌入式和数据采集技术为基础,研究设计并实现了基于ARM+FPGA体系架构面向高速实时数据采集应用的一种实用新型智能控制器。本文阐述了主处理器ARM最小系统、协处理器FPGA最小系统和ARM与FPGA通信接口等硬件系统技术的实现,以及Linux FPGA字符设备驱动程序开发、协处理器FPGA控制程序和主处理器ARM应用程序设计。智能控制器运用FPGA并行运算处理结构的优势,控制ADC进行高速数据采集。FPGA还可配置成软核处理器-Nios II嵌入式处理器,与ARM构成双核处理器系统。智能控制器通过ARM实现对FPGA的管理控制、实时数据采集和丰富外围接口的通信。

本文引用地址:http://www.amcfsurvey.com/article/249568.htm0 引言

自上世纪七十年代初以来,微处理器的诞生促进了计算机信息技术的迅速发展和应用。数据采集与处理是集智能传感器系统、信号采集调理与转换、计算机信息等技术的综合,是获取信息的重要手段。随着微处理器的普及,数据采集技术在工业领域中发挥着越来越重要的作用。

传统的数据采集设备控制器主要是以单片机和PC机为主。前者处理数据运算能力有限、实时性较差;后者成本较高、灵活性差。ARM微处理器具有体积小、成本低,功能丰富等优点。FPGA并行运算结构,I/O资源丰富,在高速实时数据处理方面优势明显。采用ARM+FPGA的系统架构,可以综合两者优势,实现数据高速实时采集与处理。

ARM与FPGA工作方式为主从模式。主处理器ARM选用美国ATMEL公司的AT91SAM9260,主频工作在180MHz时可达200MIPS的处理性能。协处理

器选用的FPGA是Altera Cyclone系列EP1C6Q240I8NFPGA。FPGA工作时钟是50MHZ,可以通过设置内部锁相环使工作时钟倍频。

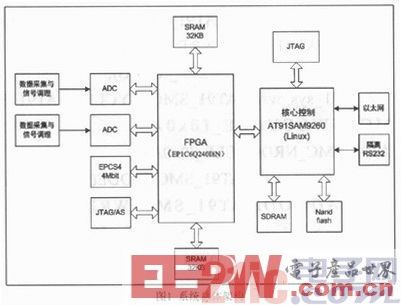

1 系统总体方案

智能控制器主要由ADC数据采集电路、FPGA最小系统、ARM最小系统三个部分构成。ADC选用单电源供电的14位的AD9240,采样率可达10 MSPS。它采用高速、低成本的CMOS工艺,分辨率和速度均达到现有混合方案的水平,而功耗与成本却低得多。协处理器选用ALTERA公司的EP1C6O240I8N芯片,通过外接两片32KB SRAM存储器、4Mbit串行配置芯片EPCS4、标准AS编程接口、JTAG调试接口构成FPGA最小系统。ARM最小系统由AT91SAM9260微处理器、运行和存储程序的1片64MBytes的SDRAM和1片256 MBytes的NandFlash、1个RS232接口和1个10/100-Base-T以太网接口构成。

系统工作原理是:首先将信号采集调理电路过来的两路信号分别送入两个ADC同步采样,ADC把模拟信号转化为14bit精度的数字信号;然后FPGA对两个通道的ADC转换后的数字信号进行预处理,采用多点采样求平均方法滤除50Hz工频干扰;最后把两个ADC采样数据存储到两片SRAM缓存中。ARM与FPGA通信采用数据总线方式,通过在Linux操作系统下开发字符型FPGA设备驱动程序,然后编译或者加载到Linux内核中,ARM可以在应用层程序读取FPGA预处理后的数据,此时FPGA内部直接把ARM的总线连接到SRAM的总线上来读取FPGA预处理后的数据。ARM可以通过以太网和RS232接口与上位机通信。

2 ARM和FPGA通信接口设计

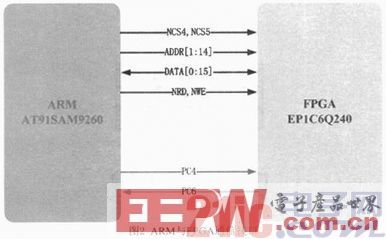

主处理器ARM所在的核心板负责整个系统的控制与管理。智能控制器与上位机的通信接口串口、以太网、CAN由此板引出。核心板与扩展板协处理器FPGA的通信采用总线方式。这种通信方式的本质是FPGA作为ARM的外设SRAM,ARM访问存储器,进行读和写操作。连接如图2所示。

ARM与FPGA通过总线相连,ARM的数据线D0:D15、地址线A1:A14和片选NCS4、NCS5与FPGA相连,另外2片SRAM直接与FPGA相连。NCS4控制读写FPGA内部状态寄存器和命令寄存器。NCS5控制FPGA读写两片SRAM中存放的数据。所有数据信息都通过DATA[0:15]双向数据总线传输。

NCS4片选有效对应ARM的地址映射为0X5000 0000-0X5000 8000,NCS5片选有效地址对应ARM的地址映射为0x60000000-0x6000 8000,FPGA此时实质上相当于ARM內部存储器。在地址范围内任意选取地址作为ARM与FPGA通信的FPGA内部寄存器地址。这些寄存器有ARM向FPGA内部写寄存器,也有ARM从FPGA内部读寄存器。

主处理器ARM要想从0X6000 0000-0x6000 8000地址范围内直接读出两片SRAM中存储的ADC采样预处理后的的数据,需要有协处理器FPGA的协助配合。

这样就明确了协处理器FPGA在与主处理器ARM通信时需要完成的任务:1)解析主处理器ARM写FPGA寄存器的命令,执行相应操作;2)将执行操作后的一些状态信息写入相应的FPGA内部寄存器供主处理器查询操作结果:3)协助配合主处理器ARM读取两片SRAM中存储的ADC采集预处理后的数据。

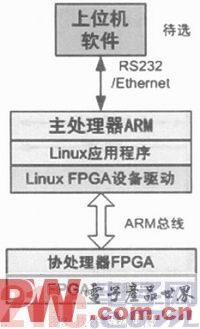

3 系统软件设计

智能控制器软件包括Linux FPGA字符型设备驱动程序、主处理器ARM应用程序、FPGA数据釆集及预处理存储程序。软件系统结构框图如图3所示。

3.1 FPGA设备驱动程序

Linux设备驱动被分为三类:字符设备、块设备和网络设备。字符设备是以字符为单位输入输出数据的设备。FPGA设备驱动程序为字符型设备驱动程序,其基本框架为:1)定义一个结构体static structfile operations变量,其內定义一些设备的打开、关闭、读、写、控制函数;2)在结构体外分别实现结构体中定义的这些函数;3)向内核中注册或删除驱动模块。Linux内核中一个字符设备用cdev数据结构来描述和管理设备文件。智能控制器的协处理器FPGA用作主处理器ARM外部静态存储器SRAM。因此,主处理器ARM可以通过静态存储控制器(SMC)产生信号控制外部存储设备或者外围接口设备来进行读写操作。FPGA字符型设备驱动程序能够完成控制FPGA模块,完成数据采集,最为关键的是初始化FPGA模块,配置主处理器ARM的SMC来实现FPGA总线驱动。可参照ARM静态存储控制器读、写时序。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

fpga相关文章:fpga是什么

linux相关文章:linux教程

锁相环相关文章:锁相环原理

评论