基于DSP与AD7656的高速AD采集系统设计

摘要:在某综合控制计算机系统中为了实现对多路AD信号实时高精度采集,采用了以B为核心,与AD7656芯片相组合的高精度、实时A/D数据采集砹计实现方案。重点分析硬件接口电路的设计、PCB设计中应注意的问题和软件设计实现流程。通过系统联试等多方验证,该设计方案实时性强,精度高,满足某综合控制计算机系统的性能指标要求。

本文引用地址:http://www.amcfsurvey.com/article/249049.htm关键词:TMS320C6713B;AD7656;接口电路

0 引言

为实现对某综合控制计算机对整个综合控制系统工作状态的实时状态监控以及故障检测,在设计中考虑到综合控制系统对监测信号精度和实时性要求较高,模拟量采集模块设计中采用了AD7656作为模/数转换芯片,该芯片支持6路通道,可同步进行模数转换,A/D转换输出可达到16位。数据处理和控制采用TI公司的TMS320C6000系列的高速32位浮点DSP芯片TMS320C6713B,该芯片通过EMIF总线接口实现对AD7656访问。

1 芯片介绍

1.1 TMS320C6713B主要特点

TMS320C6713是美国德州仪器公司(TI)推出的一款浮点32位DSP芯片,基于高性能、先进的VelociTI超长指令字体系结构,该芯片的内部结构包括如下特点:

(1)处理速度快,工作主频最高可达到200MHz,峰值运算能力为1800MIPS/1350MFLOPS450MMACS;

(2)具有8个功能单元的高级VLIW体系结构CPU,集成2个乘法器和6个ALU,指令打包减少代码数量;

(3)集成了32×32比特的乘法器,其结果可为32bit;

(4)片内存储器采用两级高速缓存结构,包括4KB的第一级高速程序缓存器(L1P)、4KB第一级高速数据缓存(L1D),第二级共256KB内存储容量(64KB的L2统一缓存/映射RAM,192KB的附加L2RAM);

(5)32位外部存储器接口(EMIF总线接口),无缝接口到SRAM、EPROM、FLASH、SBSRAM和SDRAM。

1.2 AD7656模数转换器

1.2.1 AD7656特点

AD7656是美国模拟器件公司(ADI)公司推出的一款采用iCMOS工艺制造的高集成度、6通道16位SAR型ADC,该器件具有4LSB(INL),每通道达250kSPS的采样速率,内置一个2.5V内部基准电压源和基准缓冲器。该芯片功耗仅为160mW。AD7656特点如下:1)供电电源电压:5V,±15V;2)可通过配置选择模拟量输入电压范围-10V~10V或-5V~5V;3)片内集成2.5V基准电压源和基准缓冲器;4)通道可同步采样,采样速率可达250kSPS;5)支持并行和高速串行接口访问。

1.2.2 AD7656的原理及结构

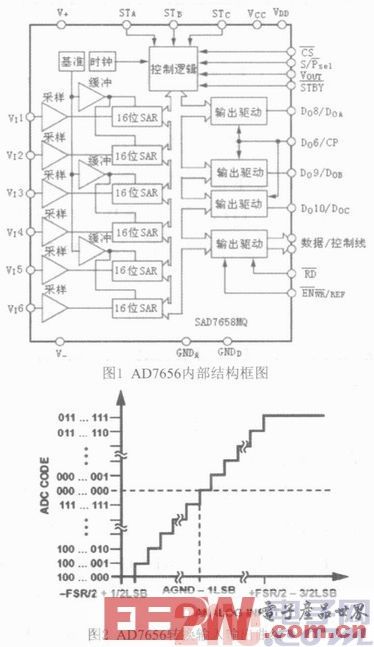

AD7656的内部结构见图1所示,AD7656内置时钟电路,外部模拟量信号从VI引脚输入,经过一个高带宽的线性跟随器(T/H)单元进行采样,保证满量程的输入正弦波时转换精度达到16位。AD7656处理的最高频率为8MHz;经过AD7656中心单元16位SAR转换,将模拟信号转换为数字信号,通过控制逻辑单元,将数字信号输出驱动。

AD7656的模拟信号输入采取了单端输入方式,输入信号的电平范围为两种±10V和±5V,可通过两种方式选择输入信号电平范围,硬件上通过RANGE管脚设置,软件上通过配置控制寄存器的RNGX位来选择。

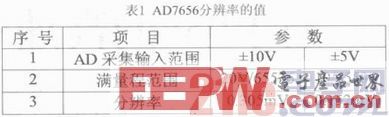

AD7656的转换后输出的数据格式见图2所示,分辨率与输入信号的范围设置有关,具体分辨率值见表1所示。

2 模拟转换电路设计

2.1 AD7656前端调理电路

由于在综合控制计算机采集的信号源与AD7656要求的输入信号不匹配,所以对信号源的信号进行前端调理电路调整,在AD7656前端调理电路设计主要考虑了如下因素:

(1)阻抗匹配。由于输入信号的信号源不一定是低阻抗,AD7656的输入端很可能会对信号源信号分压,从而影响采集转换信号的精度。在AD7656前级输入采用运算放大缓冲器解决该问题,因为运算放大缓冲器具有很高的输入阻抗,因此不会对信号源分压,同时它的低输出阻抗适合驱动AD7656的输入端;

(2)减小容性负载的影响。AD7656输入端具有容性负载特性,通常需要一个电阻和电容组成外部补偿电路,采用该电路给信号源增加了容性负载。

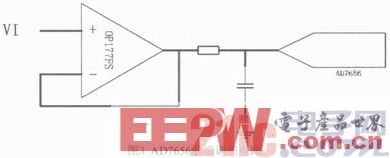

AD7656前端调理电路设计见图3所示。AD7656前端调理电路采用的运算放大缓冲器为ADI公司的OP177FS,其具有低输入失调电压(25μV),失调电压时间漂移最大0.1 μV/℃,开环增益最小12V/μV,电源电流2.0mA。

2.2 AD7656与TMS320C6713B接口电路设计

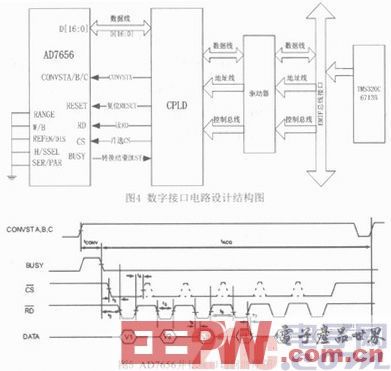

AD7656与TMS320C6713B接口电路采取并行接口设计。在电路设计时将AD7656的“SER/PAR”管脚设置为并行接口方式,“W/B”管脚设置为字方式,“H/S SEL”管脚设置为硬件启动转换方式。TMS320C6713B通过外部存储器接口(EMIF)总线实现对AD7656访问,启动对AD7656转换,读取转换结果数据,接口电路结构图见图4所示。

TMS320C6713B通过CPLD实现对AD7656控制逻辑译码,来满足AD7656的访问时信号的逻辑要求,AD7656访问时序图见图5所示。

AD7656包括6通道ADC转换,可实现6通道ADC同步转换,减少了多路ADC转换采样时间。在CPLD逻辑设计中采用同时控制“CONVSTA”

“CONVSTB”“CONVSTC”管脚输出有效完成6通道ADC通道同步转换。

根据图5所示AD76565通过“CONVSTA,B,C”信号的上升沿启动ADC转换,ADC转换过程中,“BUSY”信号为逻辑“高”标识,ADC正在转换过程中,ADC转换时钟由内部时钟产生,从“CONVSTA,B,C”信号的上升沿启动转换3 μs后ADC转换结束,“BUSY”信号为逻辑“低”表示ADC转换结束。TMS320C6713B通过EMIF总线接口完成对转换结果的读取。对AD7656芯片转换结果读取,通过“CS”片选信号和“RD”读信号控制,6个通道转换结束后,TMS320C6713B控制“CS”为有效和6个“RD”读有效信号,完成对模拟量输入“V1”信号、“V2”信号、“V3”信号、“V4”信号、“V5”信号、“V6”信号转换结果的读取。

模拟信号相关文章:什么是模拟信号

c++相关文章:c++教程

模数转换器相关文章:模数转换器工作原理

矢量控制相关文章:矢量控制原理

评论