基于FPGA的北斗QPSK信号调制器设计

摘要 为研制北斗卫星导航模拟信号源,设计实现了北斗QPSK信号调制器。文中在分析了北斗卫星导航系统B1频段信号的正交相移键控调制信号的基础上,基于软件无线电的思想,在FPGA硬件平台上实现了QPSK信号调制器,通过功率谱测试,QPSK解调和简单串口信息传输,验证了调制解调硬件单元的正确性。

本文引用地址:http://www.amcfsurvey.com/article/246645.htm北斗卫星导航系统(BeiDou Navigation SatelliteSystem)是我国正在实施的自主研发、完全独立运行的全球卫星导航系统,有着广泛的应用前景。北斗卫星导航系统信号采用正交相移键控(QPSK)调制,提高了数据传输速率,降低了信号间的相互干扰,改善了定位性能,成为目前全球卫星定位系统现代化发展的方向之一。因此对北斗卫星导航接收机的需求日益增加,为了测试验收高性能卫星导航接收机的静态性能及动态性能,需要模拟产生北斗导航系统在各种环境下的真实卫星信号。

目前,针对北斗导航系统模拟信号源的研究较少,可参考GPS和GLONASS模拟信号源的研究,分析各个导航系统之间的差别,找到合适的研究方案。文献分析了GLONASS信号的结构特点,研究了复杂环境下GLONASS导航信号的产生,文献针对GPS信号模拟源的算法进行研究,并通过FPGA实现模拟源的产生,文献分析了北斗卫星导航B1频段信号的结构,并用Simulink平台实现了信号模拟。

北斗导航系统已于2011年12月进入试运行阶段,并于2012年12月公布了空间信号接口控制文件(Interface Control Document,ICD)。本文针对ICD文件中北斗B1频段的QPSK调制信号进行结构分析,采用软件无线电的方法来研究QPSK信号的调制解调,分析QPSK信号调制解调的原理,利用FPGA仿真实现QPSK信号的调制解调,同时在射频输出端观察调制信号的功率密度谱。

1 北斗B1频段信号特征

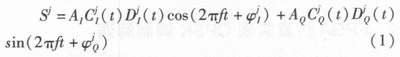

北斗B1频段信号由两个支路的“测距码+导航电文”正交调制在载波上构成。信号表达式如下

式中,j表示卫星编号;AI、AQ分别表示调制于B1频段载波同相、正交相支路的测距码振幅;CI、CQ分别表示同相、正交相支路的测距码;DI、DQ分别表示同相、正交相支路测距码上调制的数据码;f表示B1频段载波频率;φI、φQ分别表示B1频段载波同相、正交相支路的初相。

根据北斗B1频段信号QPSK调制方式的特点以及上式所示的信号结构,可知北斗B1频段每颗卫星均有一对独特的测距码,两者彼此不相关且正交,接收到同一颗卫星信号的两个支路受各种因素影响所导致的码延迟、多普勒频移等均相同。

2 北斗信号的QPSK调制

在“北斗二号”系统中,采用正交相移键控,QPSK,QPSK调制技术的核心思想是两个载波正交BPSK信号的合成,即将一个比特流的每一个四进制码元用两个二进制码元的组合来表示,两个二进制码元中的前一个码元用I表示,后一个码元用Q表示。由于在一个调制符号中传输2 Byte,QPSK调制比BPSK调制的带宽效率高一倍。载波的相位为4个间隔相等的值:π/4,3π/4,5π/4,7π/4。这种调制方式使同一载波每次可传输2 Byte信息,从而使载波的频带利用率比BPSK提高了1倍,同时抗干扰性更强。

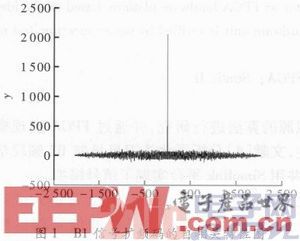

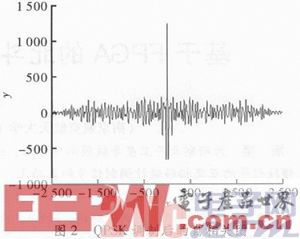

对QPSK调制后的数据进行相关运算,选取50位数据,通过仿真结果可以发现,加入QPSK调制技术后,原测距码的自相关曲线发生了变化。在QPSK调制下的测距码,除了存在一个明显的高峰外,还具有两个比较明显的次高峰,分别位于靠近主峰的左右两侧。

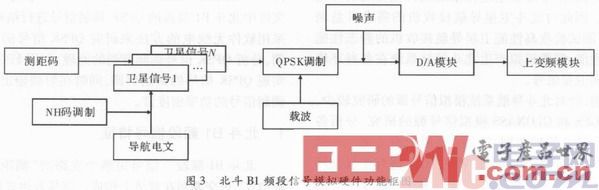

3 北斗B1频段信号的模拟

北斗B1频段数字信号生成首先按照固定的采样时间间隔,也就是固定的采样频率(采样频率取1 561.098 MHz),加入卫星的初始相位和多普勒频移,生成中频载波信号;然后将经过QPSK调制方式调制的测距码和北斗导航电文调制到载波上叠加。如果是MEO/IGSO的卫星需要在导航电文中在调制20位的NH码。每颗卫星的测距码和导航电文都不同,因此应该对每颗卫星的信号进行叠加,接着对多卫星信号的每颗卫星信号加入预设的强度,可设定的高斯白噪声,最后设定好模拟时长,将信号数据通过工作站储存模块导入到工作站保存。

4 FPGA仿真实现QPSK调制解调

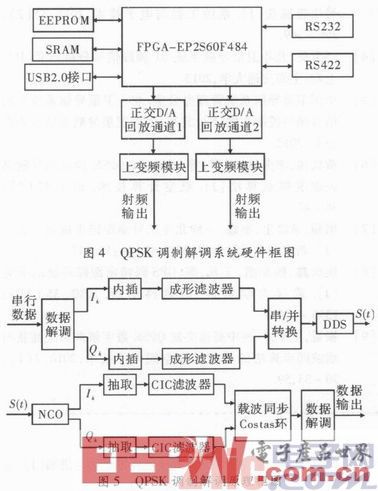

QPSK调制对输入数据流经内插、成形滤波和并串转换后,再经正交调制后即得到已调QPSK信号。内插有助于对基带信号进行波形成形,可以通过重复现存采样点或者插入零脉冲来实现,成形滤波器的作用是消除码间干扰和频谱扩散。QPSK解调对基带信号进行抽取、CIC滤波和Costas环载波同步后,再经过解调得到输出数据。采用多级CIC滤波器级联来实现较大的阻带衰减,Costas环来估计和校正解调过程中的多普勒频移。在整个设计方案中,数字调制解调算法在FPGA中完成。FPGA硬件框图如图4所示,系统原理方案如图5所示。

图5中CIC滤波器即级联积分器梳状(Cascade Integrator Comb,CIC)滤波器,滤波器的冲击响应如下形式

调制部分,数据通过串口输入,产生宽度为8 bit的并行数据流,然后分成I,Q两路数据流,经过补零内插,成形滤波和数据位截短后,通过并串转换,再通过DDS模块生成基带QPSK调制信号。调制输出数据的速率是128 kbit·s-1,而实现DDS的器件AD9857中设定输入数据速率是1 Mbit·s-1,为使两者速率匹配,设计中采用内插方法来实现。在内插模块的设计中,采用最简单的实现方法,即在数据之间插零。零的个数N由内插前后数据的速率决定,设计中N=7。内插模块通过数据锁存器和计数器实现。在内插模块设计中,由于采用了“插零”处理,导致码间干扰和带外辐射增大,为减小这些对信号解调的影响,设计采用成型滤波器。并串转换模块通过4级锁位寄存器实现,并行16位的输人数据按照并行4位的格式串行输入到DDS。

模拟信号相关文章:什么是模拟信号

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论