FPGA在多制式视频转换系统中的应用

1 引言

目前, 在军事、工业和医学领域存在着大量的非标准视频系统, 其视频信号只能在专业的设备上才能播放和录制。而实际中广泛采用的是标准电视信号(PAL ,NTSC, SECAM) 或VGA 视频, 这就给这些领域内的观测监督和学术交流造成了许多困难。以医学信号为例, 目前, 国内医院很多科室的手术监控设备都是国外进口的一体式设备, 手术影像资料只能供室内的几名医生观看, 无法通过电视系统传送到外部监测。如能将非标准视频流转换为标准视频流, 无疑会给这些领域带来很大的便利。时下的视频转换系统大多存在转换速度慢、功能单一、图像质量不高的缺点, 且一般是一机一用。本文介绍了基于单片机+ FPGA 的视频制式的转换系统, 利用单片机方便的嵌入性及灵活的可编程性, 再结合FPGA 强大的逻辑控制功能很好地克服了这些弊端, 实现了实时、高质量的视频图像转换, 同时, 可以方便地改变系统参数, 实现一机多用。

2 系统设计原理简介

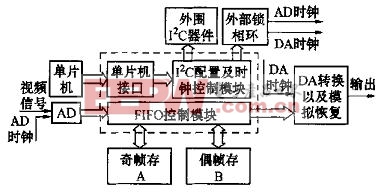

不同制式视频信号间的根本区别在于扫描方式和行场频率不同。标准VGA 采用逐行扫描, 在一帧内实现对图像的完全扫描; 标准电视信号(以PAL制为例)采用隔行扫描, 利用视觉暂留, 将奇偶场恢复成一帧完整图像。而非标准视频流则无一定规律。因此, 视频转换的基本思路是将非标准视频信号经模数转换成数字信号, 在存储器中缓存, 变频读出或经过数字信号处理, 再通过数模转换恢复成标准视频流。本系统设计思

路框图如图1 所示。

从原理可以看出, 只要数据读出速度高于写入速度, 就不会使图像产生突变现象, 从而达到实时处理的目的。设计中, 存储器采用2片512K×8 bit 的FIFOAL440, 它采用DRAM 工艺, 最高时钟可达80MHz,是专用的视频存储器。逻辑主控单元选用Altera 公司出品的FLEX10K50E 实现, 其门数达到5 万个, 处理速度最高可达220MHz, 很适合高速数据流处理。同步恢复采用74ACT715, 它可按编程数据产生隔行或逐行的电视行场同步信号, 非常适合于多制式输出系统。而视频恢复编码部分采用的是专用数字图像处理芯片DSP AL128, 其内置的高集成化数字处理器, 可以将逐行扫描数字信号直接恢复成标准电视信号和S-VIDEO 输出。

3 系统设计实现

整个系统大体框架如图2 所示, 图中虚线部分均由FPGA 实现。

3. 1 单片机接口模块

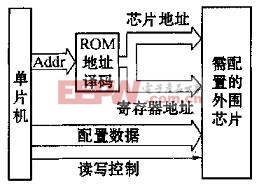

系统中有FIFO ,AL128 的I2C 参数和74ACT715的初始化参数及数模、模数时钟分频参数共计90 个,为避免出现繁琐的判断语句, 设计中采用FPGA 内置ROM 结构。其原理图如图3 所示。

图3 单片机译码原理图

FPGA 将单片机送来的机器地址(00H~5AH )译码成芯片地址, 芯片地址总共10位, 高2位用来判断配置何种芯片, 低8位用来判断配置该芯片中第N个寄存器。再结合单片机送来的数据线和读写控制线来决定对该寄存器进行读或写操作以及写入的数据。

74ACT715 的配置参数为12位, 配置中用两个连续的地址分别记录其高4位和低8位数据。其中, 57H~5AH为只读地址, 相应数据将控制数模、模数时钟的频率。

3. 2 I2C 配置及时钟控制模块

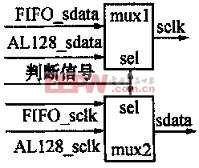

本系统FPGA 的一个重要功能就是对芯片初始化和I2C 参数配置。I2C 总线是一种由飞利浦公司开发的接口总线, 利用一条数据线sdata 和一条时钟线sclk 在主从器件间进行串行通信。飞利浦公司制定了标准I2C协议, 但是, 工业上依然使用很多非标准I2C器件, 本系统的FIFO、AL128 均为非标准I2C 器件, 故要对它们分别进行配置, 利用FPGA 的逻辑控制及内置MUX 可以在不同读写时序间灵活切换, 达到对多个芯片的全双工同步数据传输。实现原理图如图4 所示。

图4 总线切换控制原理图

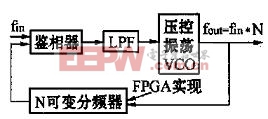

同时, 由系统实现原理分析可知, 视频制式变换的关键在于扫描频率变化, 即,AD采样时钟频率和DA图像恢复时钟频率。这部分数字频率在系统中是由外部锁相环(PLL) 和FPGA 中的可变分频计数器实现的。其原理图如图5 所示。

图5 数字锁相环原理图

与普通锁相环不同的是, 利用FPGA 的可编程性, PLL的参考频率可以由单片机配置的分频数随意更改, 使数字频率合成电路有较高的稳定性、灵活性和灵敏度。

3. 3 FIFO 控制模块

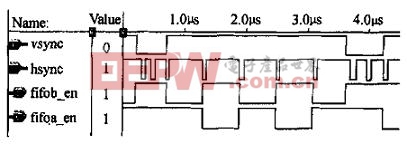

考虑到非标准视频信号一帧图像数据量太大, 一块FIFO 放不下, 同时, 电视信号都采用隔行扫描, 数据流将按奇偶场交替输出, 故设计中用两块FIFO A、B 分别存放图像的奇偶帧, 但在图像恢复时为逐行扫描方式, 这就涉及到在两块FIFO 间交替读出数据的问题。设计中, 用两个场同步信号Vsync 间的行同步信号Hsync 做判断, 决定两块F IFO 的读写, 使数据按ABAB..... 逐行读出。该部分代码段如下, 仿真时序图见图6。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ctrl IS

PORT (

vsync, hsync : IN STD_LOGIC;

fifoa_en, fifob_en:OUT STD_LOGIC

);

END ctrl;

ARCHITECTURE behav OF ctrl IS

SIGNAL fifo_en: STD_LOGIC;

BEGIN

PROCESS (hsync, vsync)

BEGIN

IF vsync=''0'' THEN

fifo_en= ''1'

ELSIF hsync''event AND hsync=''0'' THEN

fifo_en= not (fifo_en);

END IF;

END PROCESS;

fifoa_en= fifo_en WHEN vsync=''1'' ELSE ''1'

fifob_en= not (fifo_en) WHEN vsync=''1'' ELSE ''1'

END behav;

图6 仿真时序图

在时钟方面, FIFO 写入时钟与AD 采样时钟相等,FIFO 读出时钟与DA 恢复像素时钟相等。实时处理运动帧时, 为不在两场之间出现跳动现象, 读出时钟要高于写入时钟。在实际应用中, 为了产生分频率1024×768, 刷新频率为60 Hz 的VGA 图像, 读出时钟高达46MHz,这样的高速数据处理就必须满足一定的时延要求。以50MHz 时钟为例, 数据与时钟间的最大时延不能超过10ns (像素时钟20ns, 半周期为10ns)。经过FGPA 的Quartus 综合分析, 时钟与数据间的最大延时为3.7ns, 满足系统时延要求。一般地, 这一数据是系统最坏情况下的延时, 实际系统延时将小于仿真数据。

4 结束语

在数字电路设计中, FPGA 发挥了越来越重要的作用, 随着FPGA 向高密度、低成本方向发展, 目前的一个趋势是把系统级功能放到FPGA 器件中。本文介绍的视频转换系统以FPGA 作为系统主控元件, 不但大大减少了电路版尺寸, 而且增强了系统可靠性和灵活性。在实际测试中, 将非标准隔行视频信号(1024行, 50Hz 场频) 成功地转换成了高清晰度的VGA 图像和标准PAL 电视图像。目前, 该系统已应用于某医院监视系统。

评论