基于DSP Builder的脑电信号小波处理

1 引言

脑电信号EEG(Electroencephalograph)是人体一种基本生理信号,具有重要的临床诊断和医疗价值。南于脑电信号自身具有非平稳性随机的特点,因此,对其实时滤波具有相当难度。自从Berger 1929年发现脑电信号以来,人们采用多种数字信号处理技术处理分析脑电信号,由于传统的滤波去噪方法所用滤波器一般具有低通特性,因此采用经典滤波法对非平稳信号去噪,降低噪声,展宽波形,平滑信号中突变尖峰的成分,但可能损失这些突变点携带的重要信息,而傅里叶频谱分析仅是一种纯频率分析方法,该方法对时变的非平稳脑电信号无效。

与传统的傅里叶变换相比较,小波变换是一种多尺度信号分析方法,具有良好的时频局部化特性,非常适合分析非平稳信号的瞬态特性和时变特性,这正是分析 EEG所需要的,EEG中许多病变都是以瞬态形式表现的。只有结合时间和频率进行处理,才能取得更好效果。但小波分解每次只分解上次分解的低频部分,而不分解高频部分,所以高频段分辨率较差。而小波包分解是一种从小波分解延伸出的更细致的分解和重构信号的方法,它不但分解低频部分,而且还能二次分解高频部分,能够很好地将频率分辨率调整到与脑电节律特性相一致,因此小波包分解具有更好的滤波特性。若将小波包方法引入脑电信号分析.不仅可以克服传统脑电分析的不足.还可以改进Mallat算法分析实际脑电中的不足。

脑电信号的数字处理以往采用通用PC机或单片机实现,存在实时性差等缺点。随之,基于FPGA的小波变换在脑电信号数字处理中应运而生,其实时性好。 DSP Builder将Matlab/Simulink设计仿真工具的算法开发、模拟和验证功能和Quartus II软件的HDL综合、模拟和验证功能相结合,为小波变换的FPGA提供良好的平台。

2 一维离散小波(1D-DWT)Mallat改进算法

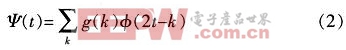

多分辨率分析是小波分析的核心理论,其Mallat算法是信号小波分解和重构的常用算法。正交小波的分解和重构公式由尺度函数的尺度方程系数确定。假设构造正交小波的尺度函数φ(t)的两尺度方程为:

![]()

式中,g(n)=(-1)n-1h(2N-n-1),N为自然数常数。

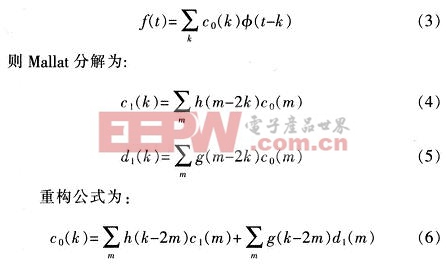

设信号为:

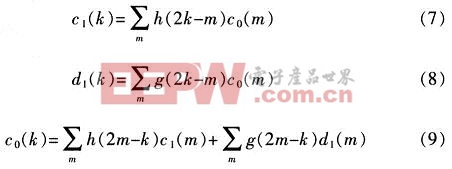

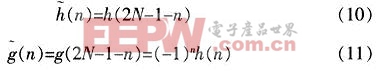

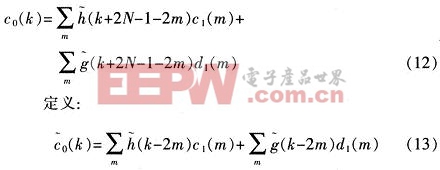

由于φ(-t)和φ(t-s)为构造正交小波的多分辨率分析尺度函数,因此上述分解和重构公式中取h(n)为h(-n)或h(n-s)均可。为了讨论方便,且不失一般性,可将上述分解公式和重构公式重写为:

带入式(9)得:

则c0(k)=c0(k-2N-1),式(13)得到的信号是式(12)得到信号的延迟。由于序列h(n)和g(n)为因果序列,所以式(13)对应的滤波器为因果滤波器。采用式(7)和式(8)继续分解信号低频分量或低频分量与高频分量.可得多级分解或小波包分解。

3 基于DSP Builder的小波变换设计实现

考虑到瞬态脉冲信号的短时性,选择具有紧支集的Daubenchies小波作为分析小波,这样有利于突出瞬态信号特征,DB小波函数具有良好的正交性和紧支撑性,可较好地表现频域信号的连续性和突变性,在实际工程应用中效果较好。故这里采用DB小波对脑电信号进行4级分解重构。滤除脑电信号中存在的直流成分或缓慢基线漂移。选取DB2小波,此时M=3,且低通滤波系数(尺度函数系数)如下:

由于浮点数在FPGA中实现比较复杂,为了减少FPGA的运算量和资源,可将滤波计算转换为整数运算和移位运算,为此首先需将以上滤波器系数转化为整数,对每个滤波器系数采用16位字长进行量化,即乘以215后取整数,而对滤波器的输出信号有移15位即得到实际输出。

以DSP Builder为平台,对式(7)、式(8)和式(13)算法进行系统级建模、仿真,再利用Signal Compiler生成HDL文件,然后利用Quartus II进行时序仿真验证。

3.1 DSP Builder实现lD-DWT分解

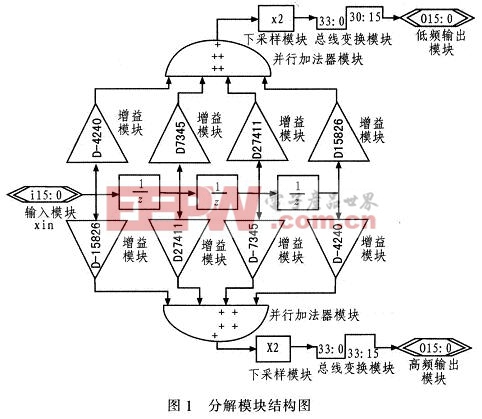

分解模块的结构如图1所示。信号并行从4级延迟线输出,与FIR滤波器系数进行卷积,然后再偶抽取便可得到近似部分和细节部分的结果。二次抽取模块采用DSP Builder的下采样模块,利用Signal Compiler生成HDL文件。

为了减少系统耗用的硬件资源,舍去输出结果的低8位,保证分解前后信号保持同样能量级。从图1中可知,各个子模块并行工作,子模块之间无需任何交叉信号,数据从输入端以流水线的方式向后传递,实现实时流水线工作。二级分解模块的设计原理同一级分解模块。

3.2 DSP Builder实现1D-DWT重构

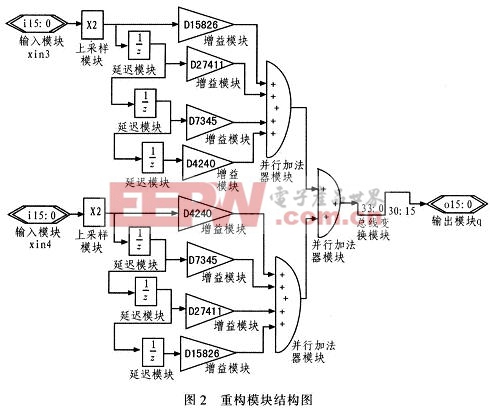

由Mallat算法可知重构模块的结构如图2所示。首先对信号二次插值,然后信号并行从四级延迟线输出,分别与FIR滤波器系数进行卷积,与分解不同的是重构有两路信号输入,经过四级延迟后并行分别与FIR滤波器卷积,得到的结果再叠加便可得到重构信号,接着利用Signal Compiler生成HDL文件,重构模块也是以流水线方式工作的。二次捕值模块由DSP Builder的上采样模块实现。

4 仿真与设计

选定一组原始数据[1,2,3,4,5,6,7,8,9,10,11…],同时作为输入信号,利用图1生成的HDL文件,在Quartus II环境下时序仿真,图3为一级小波分解时序仿真波形。利用图2生成的HDL文件,同时把图3低频高频的输出结果作为重构输入数据,进行一级小波重构仿真,仿真波形如图4所示。由图3、图4可以看出,重建后波形除有延迟外,其重建波形无失真,并能完美重构原信号,即输入、输出满足q(n)=xin(n- k)。

利用小波变换的多尺度分解和重构方法滤除信号的某些成分(高频或低频),采用DB2小波对脑电信号进行四级小波包分解,按照小波包分解原理,级联一级分解模块,每经一次分解输入的一串数据降为原来的一半.采用分频模块控制各级时钟信号,分频模块由VHDL语言编写生成.同步输出3个时钟信号,以此作为后三级分解的时钟输入信号。然后对分解后的输出信号进行四级小波包重构,按同样方式处理,级联一级重构模块,每重构一次输出数据都增为原来的2倍。尝试采用锁相环控制各级时钟信号,锁相环由Quartus II自带的功能模块实现,同时输出3个倍频时钟信号,作为后i级重构部分的输入时钟信号。

5 结论

利用信号的小波包分解高分辨率的时频关系.在滤波部分选取因果滤波器对脑电信号进行实时滤波。在DSP Builder平台上,结合Mallat算法和模块化设计原则,设计出基于FPGA的流水线结构小波变换系统,这种自上而下的高度模块化设计方法使得系统的升级改动相当方便,将这种基于FPGA的小波变换系统设计应用于脑电信号的实时滤波,是今后的研究方向。

评论