基于SA1110的掌上电脑显示器的设计与实现

随着以网络为代表的新经济时代的到来,PC已失去昔日的光采,智能3C产品(Computer、Communication and Consumer)将掀起新的一波巨浪。掌上电脑作为智能3C产品的代表之一,以其传输迅速、应用方便、功能多样等特点,正成为市场的主流产品,深受消费者的青睐。

目前,掌上电脑CPU中比较流行的有MIPS系列、SuperH系列、DragonBall系列以及ARM系列。在操作系统领域,除了部分采用Linux和自行开发的操作系统外,大部分产品采用Palm OS、Windows CE和EPOC操作系统。

为了在掌上电脑这一嵌入式系统的主要应用领域中占有一席之地,清华大学自动化系和深圳翔龙公司决定开发具有民族自主知识产权的掌上电脑。这就需要选好和开发出自己的硬件平台;同时还要开发自己的嵌入式Linux操作系统;在硬件平台和操作系统之上,再开发各种具体的应用程序,以满足特定用户的需求。本文介绍的液晶显示器的设计是整个系统设计的重要组成部分。

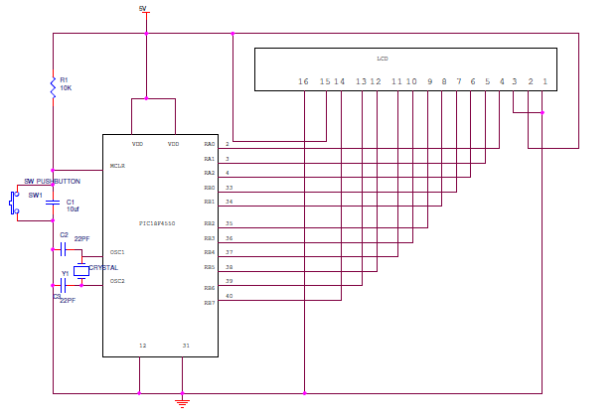

1 硬件电路组成

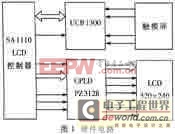

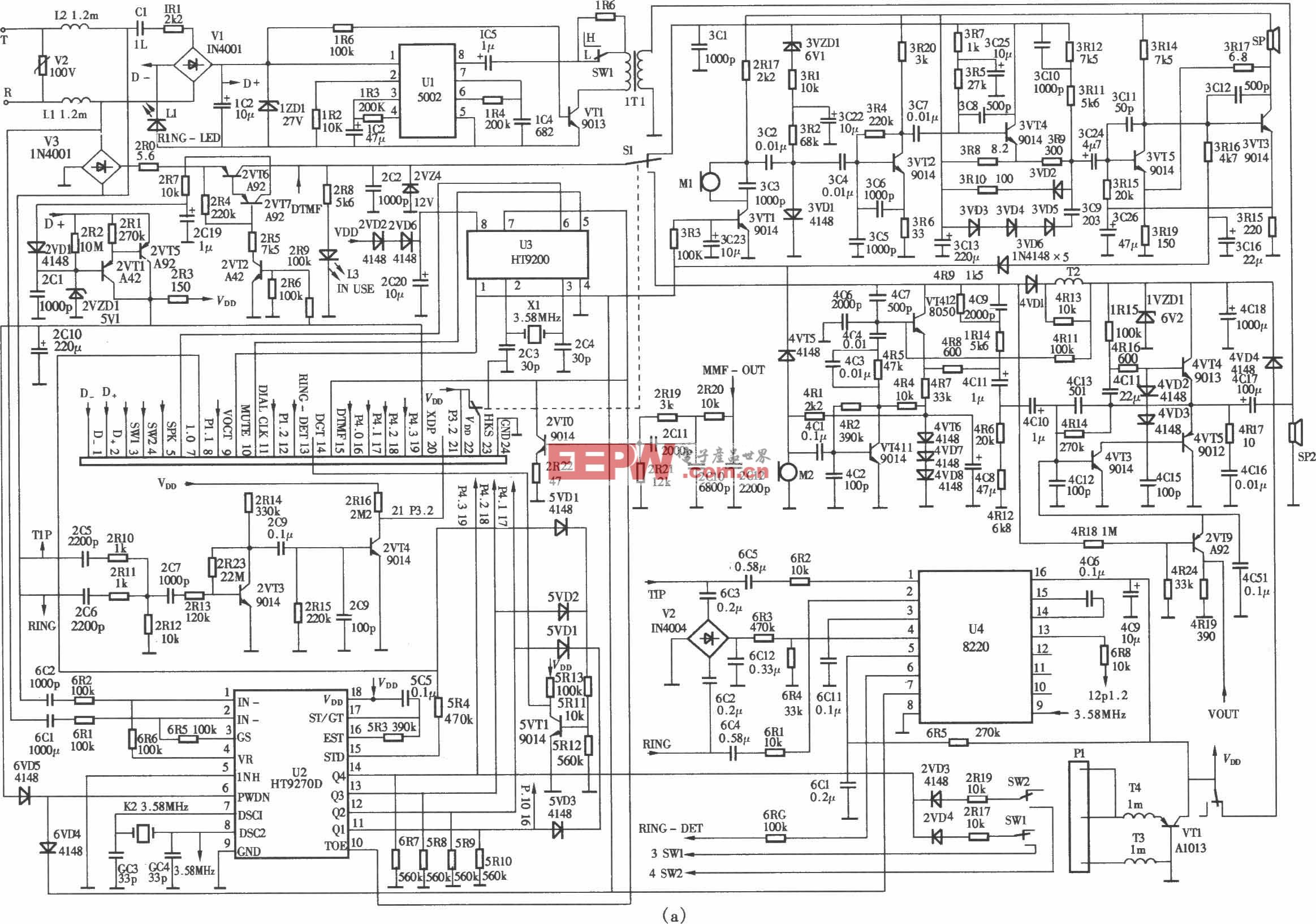

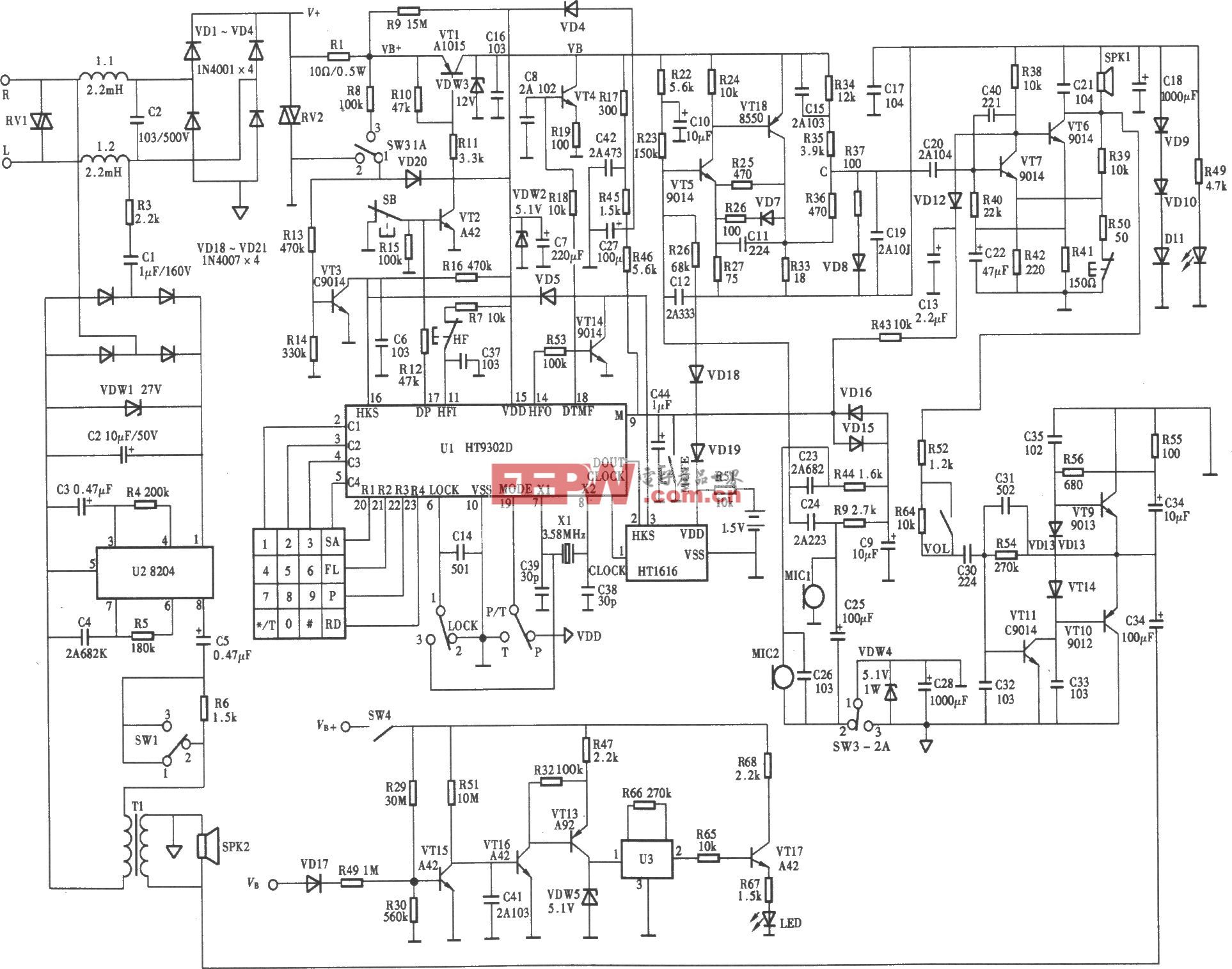

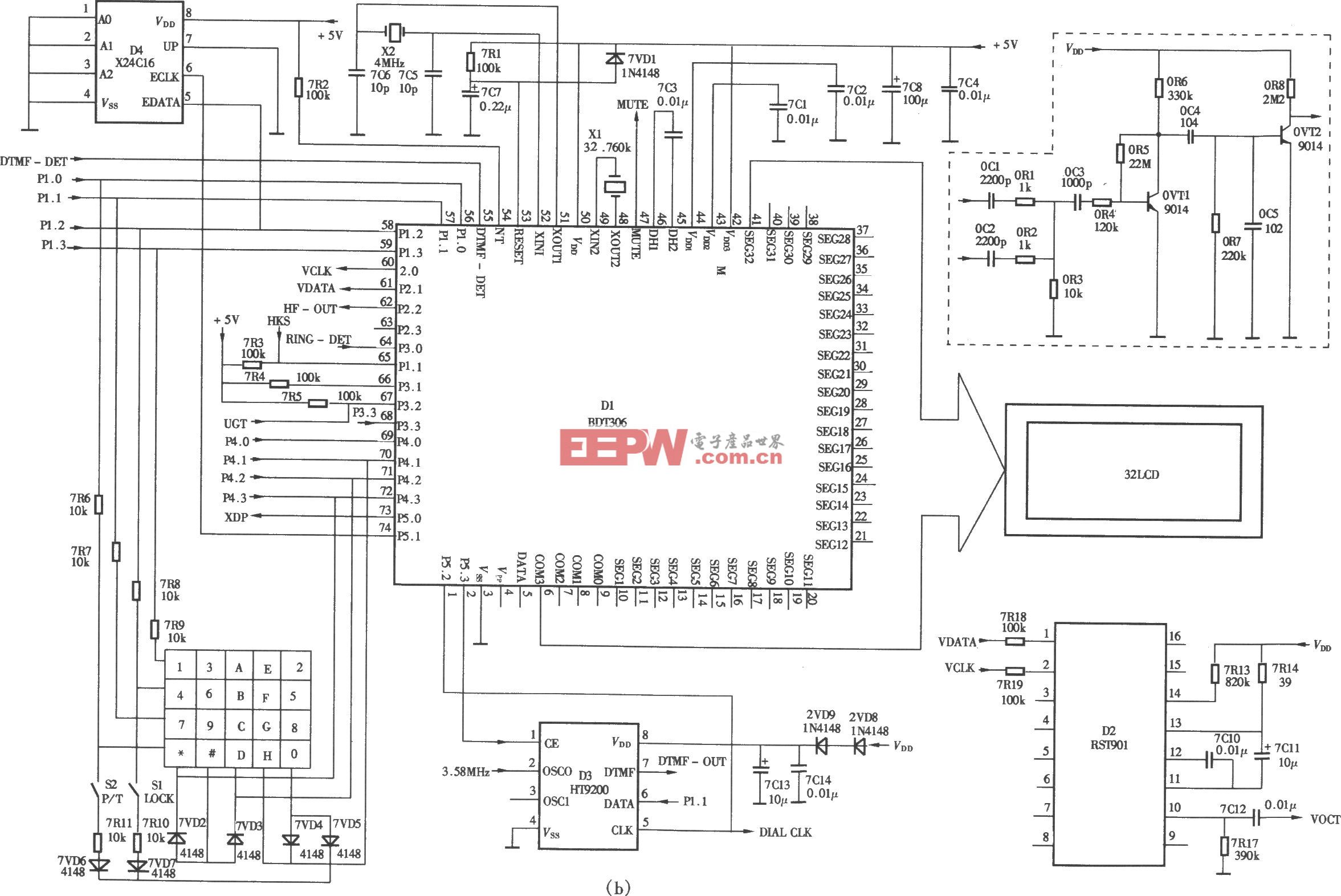

基于SA1110微处理器的掌上电脑液晶显示器的硬件电路如图1所示。主要由三部分组成:LCD控制器、专用集成电路芯片CPLD和液晶显示屏LCD。

2 SA1110的 LCD控制器

SA1110芯片内部集成了LCD控制器,该控制器有三种显示类型

·无源彩色模式:支持3375种彩色每帧允许显示256种彩色;

·有源彩色模式:支持高达65536种彩色(16位);

·无源黑白模式: 支持15级灰度。

LCD控制器支持高达1024×1024象素的显屏。然而在帧存储器中,由于存储器的总线宽度、象素编码数据的大小限制了LCD能驱动的显示屏幕的大小。LCD控制器也支持单屏和双屏显示。象素编码数据存储在外部存储器中,LCD的双通道DMA控制器可根据具体情况把数据装入一个5单元(32位长)的队列缓冲器中。DMA控制器的一个通道用于单屏显示,另一个用于双屏显示。

在帧存储器中,存储着象素编码数据。LCD控制器将其用作指针去索引一个256单元12位宽的调色板。黑白调色板4位宽,彩色调色板12位宽。来自帧存储器的象素编码数据(4位)寻址黑白调色板的顶部16单元;8位象素编码数据可访问调色板中的256单元的任意一个。在无源彩色12位象素模式下,彩色象素数据旁路掉彩色调色板并且直接送到LCD的抖动逻辑电路。在有源彩色16位象素模式下,彩色象素数据不仅旁路掉彩色调色板,而且旁路掉LCD 的抖动逻辑电路,并直接送到LCD的数据管脚。一旦4位或8位的象素编码数据选定了一个调色板单元,在这个单元中被编码的值就被传送到抖动逻辑电路。抖动逻辑电路使用一种空基和时基算法产生输出到屏幕的象素数据。抖动逻辑促使每一个象素以不同的速率在每一帧上关断,从而给黑白屏产生15级灰度,为彩色屏幕的红、绿、蓝三基色中的每一种都产生15级色度,总计为3375种彩色(每帧可获得256种彩色)。来自抖动逻辑电路的输出数据在被输出到LCD引脚和象素时钟驱动显示器之前,被放置在一个9单元的引脚数据队列缓冲区内。

根据所使用的显示屏类型,可将LCD控制器编程为4位、8位或16位的象素数据引脚。单屏黑白显示器在每个象素时钟周期内既可以采用4位也可以采用8位的数据引脚去输出4位或8位的象素。单屏彩色显示器可以采用8位的数据引脚在每个象素时钟周期内去输出2~2/3位的象素(8引脚/3种色彩/每个象素)。LCD控制器也支持双屏显示。双屏显示促使LCD控制器数据行被分成两组,一组驱动上半屏,另一组驱动下半屏。

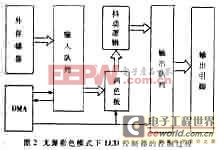

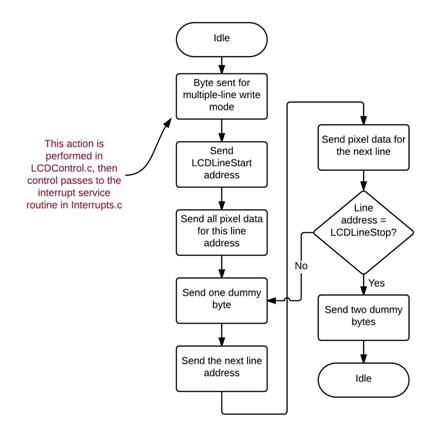

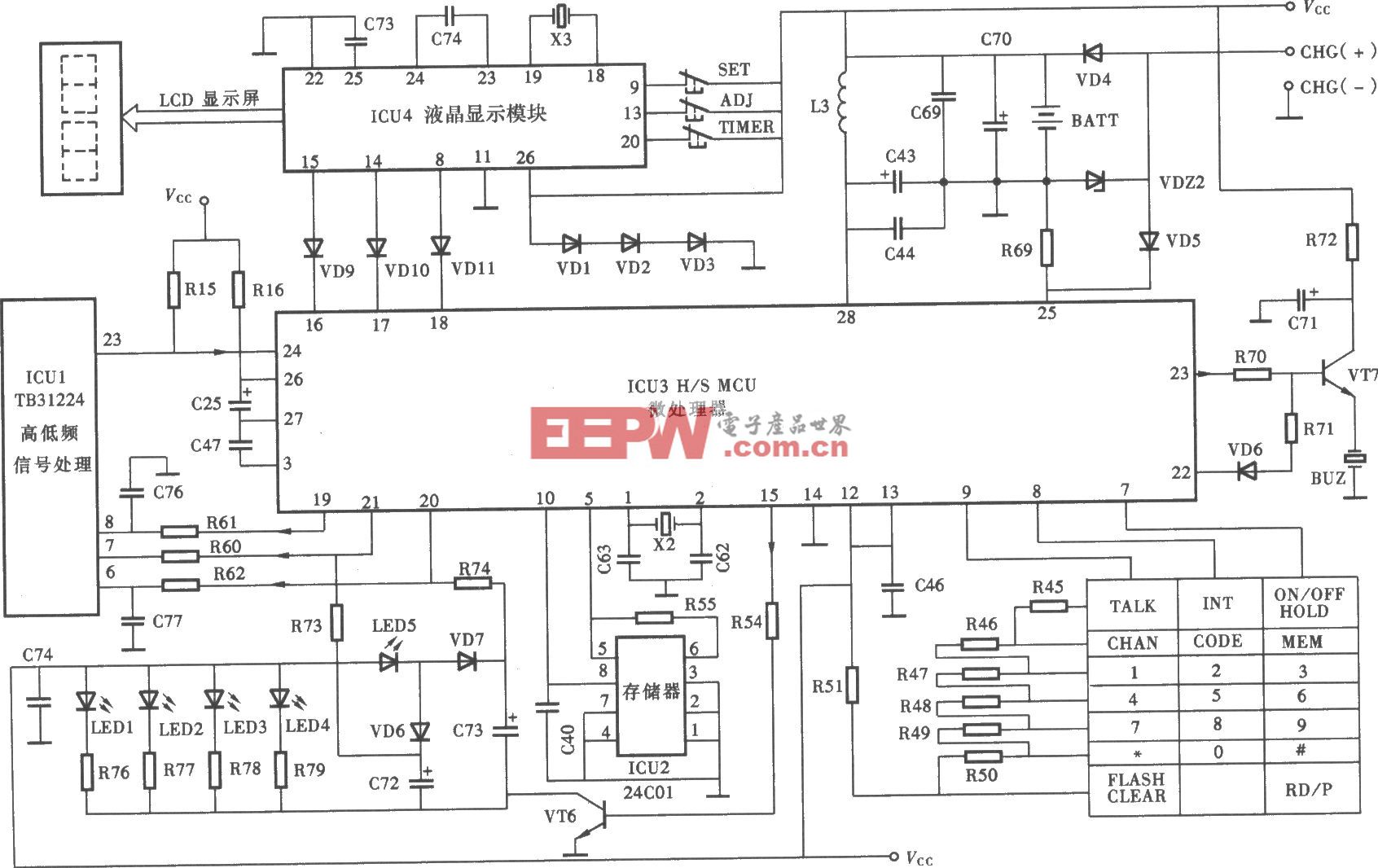

在此方案中选择了无源彩色模式。在此模式下,SA1110 LCD控制器的控制过程如图2所示。

CPLD PZ3128是Philips公司的专用集成芯片。由于手持设备的液晶显示屏种类繁多,各厂家的标准不一致使SA1110的LCD控制器与SHARP公司的3.9寸TFT有源型彩色液晶显示器在数据格式及显示时序上无法匹配。因此,对CPLD PZ3128编程可为不同数据格式的数据接口进行映射为不同类型的LCD屏配置专用的ASIC芯片。

SA1110 LCD控制器由以下引脚组成:

·LDD 0~7 :7位数据线用于4位和8位显示模式,同时也是16位TFT方式的低8位;

·GPIO 2~9:当采用的液晶模块是16位TFT方式时,构成数据线的高8位;

·L_PCLK:点时钟(Pixel clock),用于把每一点的数据送入移位寄存器;

·L_LCLK:行时钟(Line clock),用于指示一行数据由移位寄存器到显示驱动芯片传输完毕,并使得行指针加1。在16位TFT方式下,就是水平同步信号;

·L_FCLK:帧时钟(Frame clock),用于指示一帧图像的开始,同时把行指针置于显示屏的第一行。在16位TFT方式下,就是垂直同步信号;

·L_BIAS:在16位TFT方式下,输出允许信号,用于指示数据信号在时钟信号的同步下,锁存到引脚。

为了显示一帧图像,SA1110 LCD控制器首先在RAM中开辟一片缓冲区作为帧缓冲(FRAME BUFFER)。存入要显示的图像数据,然后让LCD 控制器的DMA地址寄存器指向FRAME BUFFER的起始地址,读出FRAME BUFFER中的数据到输入先入先出队列(INPUT FIFO)。由于在本设计中采用16位方式,无需对帧缓冲中的数据进行解码,所以LCD控制器不处理直接把数据送到输出先入先出队列(OUTPUT FIFO)。OUTPUT FIFO再将数据通过引脚送到CPLD 以驱动液晶显示。由于SA1110 的LCD控制器拥有自己独立的双通道DMA,同时选用了高性能SDRAM,能满足显示带宽的需求。

评论