USB 2.0高速端口的ESD保护

通用串行总线(USB)高速数据应用也十分普遍,用户在热插拨任何USB外设时可能会导致ESD事件。此外,在离导电表面几英寸的地方也可能发生空气放电,可能损坏USB接口及芯片。因此,设计人员必须为USB元件提供ESD保护。

业界制定了不少针对不同瞬态干扰的ESD标准,比如针对系统级ESD事件的IEC61000-4-2国际标准。另外还有一些元器件级的ESD敏感度测试标准,如人体模型(HBM)和机器模型(MM)等。USB 2.0高速数据线路应用的半导体ESD保护元件应当具备下列重要特性: 极低电容:将USB 2.0高速数据线路(480 Mbps)中的信号衰减减至最小; 快速动作响应时间(纳秒级):在ESD脉冲信号快速上升时保护USB元件; 低泄漏电流:将额定工作条件下的功率消耗减至最低; 强固性:能够承受很多次的ESD事件冲击而不受损伤; 小封装:集成型更小封装 本文介绍安森美半导体的新的低电容瞬态电压抑制器(TVS)二极管阵列NUP4114UPXV6的主要特性,并讨论如何为USB 2.0高速数据线路提供有效的ESD保护。

NUP4114UPXV6的特性及配置选择

NUP4114UPXV6是一款非常适合USB 2.0高速数据线路ESD保护的TVS二极管阵列。该器件具有0.8pF的极低电容(I/O线路与地之间的典型电容),能将USB 2.0高速数据线路中的信号衰减降至最低。该器件满足13 kV接触放电的系统级IEC61000-4-2标准,并能承受人体模型3B类(超过8 kV)和机器模型C类(超过400V)的CMOS器件级ESD额定脉冲,具有强固的ESD保护性能。此外,它采用SOT563封装,尺寸仅为1.6×1.6×0.55mm,非常适合计算机、手机、MP3播放器等应用中的USB2.0高速数据线路及其它高速应用的ESD保护。

NUP4114UPXV6能够保护多达4条数据线路,驱使瞬态过压达到钳位参考点,让应用免受瞬态过压条件影响。无论什么时候,只要受保护线路上的电压超过参考电压(Vf或VCC+Vf),器件中的控向(steering)二极管将正向偏置。这些二极管会迫使瞬态电流不经过敏感的CMOS芯片,而从其旁路流过。

在保护应用中,数据线路连接至这器件的引脚1、3、4和6。负参考连接至引脚2,且该引脚必须通过接地层(ground plane)直接连接至地,从而将印制电路板(PCB)的接地电感降至最低。为将寄生电感降至最低,尽可能缩短走线(trace)长度也非常重要。

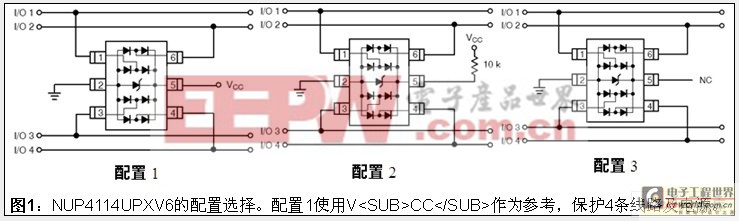

NUP4114UPXV6有3种配置选择。配置选择1采用VCC作为参考,保护4条线路及电源(图1)。在这种配置中,引脚5直接连接至正电源输入端(VCC),数据线路以电源电压为参考。内部的TVS二极管防止电源输入端上出现过压。控向二极管的偏置可降低它们的电容。

配置选择2采用偏置及电源隔离电阻来保护4条数据线路。该器件可在引脚5与VCC之间串联10kΩ电阻实现与电源隔离。这将在内部TVS及控向二极管上维持偏置,并降低它们的电容。

配置选择3采用内部TVS二极管作为参考来保护4条数据线路。在缺乏正电源参考的应用,或是需要完全隔离型电源的应用中,可以采用内部TVS作为参考。在这些应用中,引脚5不连接。采用这种配置时,只要受保护线路上的电压超过TVS工作电压与一个二极管压降的和(VC= Vf +VTVS)时,控向二极管导通。

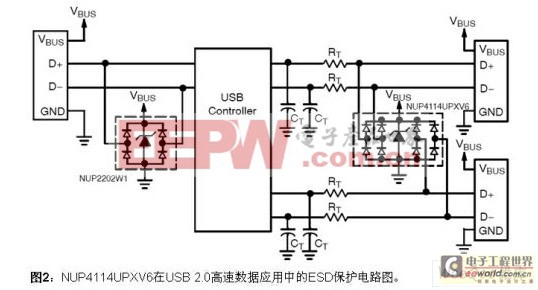

利用NUP4114UPXV6保护USB 2.0高速数据应用 USB端口由4条线路组成,其中D+和D-用于双向数据传输,其余2条线路用于总线电压及接地。图2是NUP4114UPXV6为USB2.0高速数据应用提供ESD保护的电路图。

USB控制器

如果发生ESD瞬态事件,器件中的控向二极管使瞬态电流避开受保护的IC,而集成的TVS器件将浪涌电流转移到地。TVS元件还会抑制电压总线(VBUS)上的ESD事件。NUP4114UPXV6通过这些方式保护USB 2.0高速数据线路应用中的敏感IC。

其它USB 2.0高速应用ESD保护方案

NUP4114UPXV6是一款集成型方案,用于保护2条USB 2.0高速数据线路。图2所示的USB 2.0应用不带识别(ID)线路。这类不带ID线路的USB 2.0应用除了可以采用NUP4114UPXV6之外,还可以采用安森美半导体的另一款集成型解决方案NUP2114。此外,这类应用中还可以采用不同的分立方案,比如搭配2颗安森美半导体的ESD9L和1颗ESD9X,或者搭配1颗ESD7L和1颗ESD9X,或者搭配1颗最新的ESD11L和1颗ESD9X。

此外,在带ID线路的USB 2.0应用(见图3a)中,同样可以采用安森美半导体的分立或集成ESD保护方案。比如搭配3颗ESD9L和1颗ESD9X作为分立ESD保护方案,或者采用单颗的NUP3115UP或NUP4114UP这样的集成方案,如图3所示。

本文小结

速率高达480Mbps的USB 2.0高速数据线路应用需要有效的ESD保护。安森美半导体的低电容TVS二极管阵列NUP4114UPXV6提供0.8pF的极低电容,能高速应用中的信号衰减降至极低。它提供3种不同的配置选择,可保护多达4条数据线路,让应用免受瞬态过压的影响,并迫使瞬态电流避免流过敏感的CMOS芯片。此外,该器件还符合IEC61000-4-2标准及HBM和MM测试标准。因此,设计人员可以利用该器件为USB 2.0高速应用提供有效的ESD保护。

评论