ADS8364与TMS320F2812的接口设计方案

1 芯片简介

ADS8364是美国TI公司的一种高速、低能耗、6通道同步采样转换,单十5V供电的16位高速并行接口的高性能模数转换芯片,片上带2.5V基准电压源,可用作ADS8364的参考电压。每片ADS8364实际由3个转换速率为250kb/s(当外部时钟为5MHz)的ADC构成,每个ADC有2个模拟输入通道,每个通道都有采样保持器,3个ADC组成3对模拟输入端,可同时对其中的1~3对输入信号同时采样保持,然后逐个转换。由于6个通道可以同时采样,适用于需同时采集多种信号的场合。

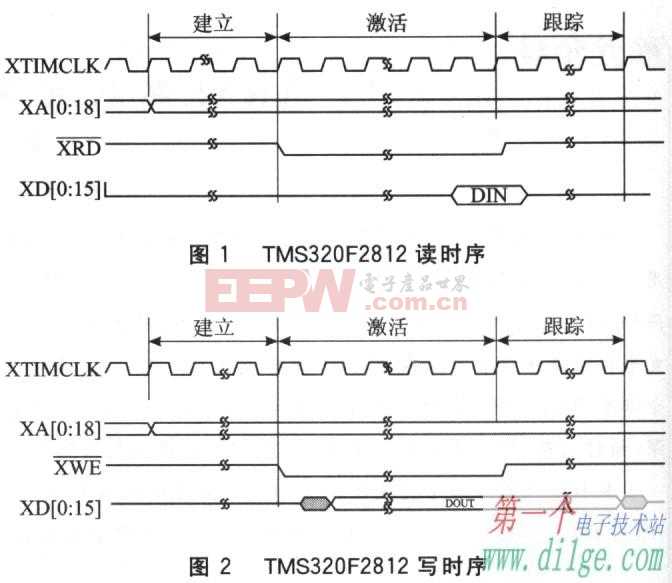

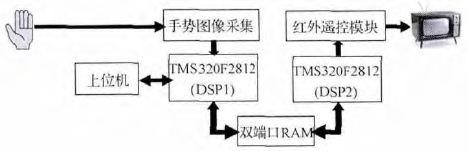

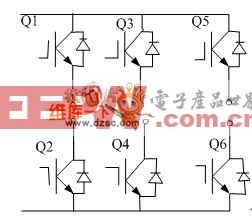

TMS320F2812是TI公司推出的一款用于控制系统的高性能、多功能、高性价比的32位定点DSP芯片。TMS320F2812采用哈佛总线结构,具有密码保护机制,可在一个周期内进行双16×16乘加和32×32乘加操作,从而兼顾控制和快速运算的双重功能;芯片上集成了多种外设,尤其是2个事件管理器为电动机以及功率变换控制提供了很大的便利,特别适用于有大批量数据处理的测控场合。

2 ADS8364的工作原理

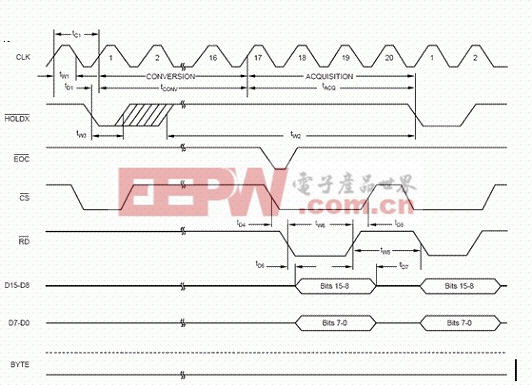

ADS8364的最大工作频率可达5MHz,采样/转换可在20个转换时钟周期内完成。ADS8364的六个通道可以同时进行采样/转换。吞吐率最大可达250ksps。ADS8364采用+5V工作电压,并带有80DB共模抑制的全差分输入通道以及六个4μs连续近似的模数转换器、六个差分采样放大器。另外,在REFIN和REFOUT引脚内部还带有+2.5V参考电压。ADS8364的差分输入可在-VREF到+VREF之间变化。三个保持信号(HOLDA、HOLDB、HOLDC)可以启动指定通道的转换。当三个保持信号同时被选通时,其转换结果将保存在六个寄存器中。对于每一个读操作,ADS8364均输出十六位数据,地址/模式信号(A0,A1,A2)可以选择如何从ADS8364读取数据,也可以选择单通道、单周期或FIFO模式。在ADS8364的HOLDX保持至少20ns的低电平时,转换开始。当转换结果被存入输出寄存器后,引脚EOC的输出将保持半个时钟周期的低电平。另外,通过置RD和CS为低电平可使数据读出到并行输出总线。

ADS8364工作时序图

3 ADS8364与TMS320F2812的接口电路

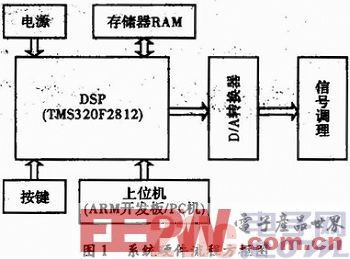

3.1 TMS320F2812的最小系统设计

(1)电源和复位部分:本设计采用外部5V直流电压供电。通过DC/DC器件产生3.3V的内核电压VDD和1.8V的I/O电压VDDIO电压。电源芯片TPS767D318为双电源输出,一路为3.3V、一路为1.8V。每路电源的最大输出电流为1A。本设计的复位信号分两种:上电复位、手动复位。上电复位由芯片TPS767D318产生,手动复位由电阻电容组成的电路产生。

(2)时钟部分:为DSP芯片提供时钟一般有两种方法。一种是采用晶体,一种是采用外部有源时钟芯片。本设计采用前者。它利用了DSP芯片内部所提供的晶振电路,在DSP芯片的X1和X2之间连接一晶体可启动内部振荡器。

(3)仿真部分:这一部分将作为程序的调试和烧录所用。2812芯片提供了5个标准的JTAG信号(TRST、TCK、TMS、TDI、TDO)和两个仿真引脚(EMU0、EMU1)。

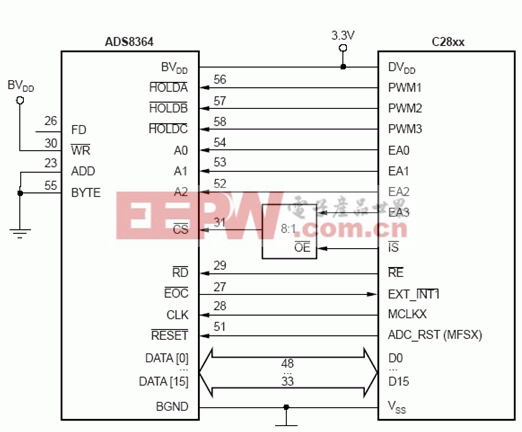

3.2 ADS8364的接口设计

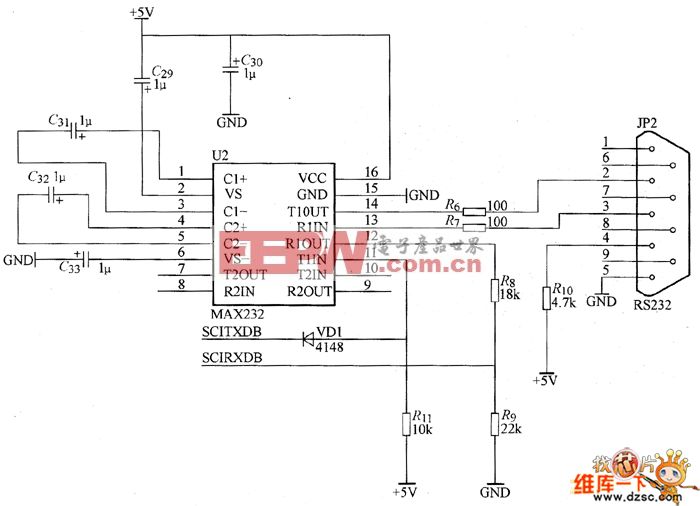

ADS8364采用+5V模拟电源(AVDD)和数字电源(DVDD),而其内部的缓冲器采用与TMS320F2812相同的+3.3V电压。缓冲器电压(BVDD)允许直接连接到3V或5V电压系统。TMS320F2812的I/O电压为+3.3V,因此,若使用该元件,ADS8364的BVDD必须设置成3.3V。

将ADS8364的BYTE引脚接到VCC上,可以使能字节模式。在这个模式中,要从模拟中正确地读取数据,需要对每个通道进行两次连续的读操作。第一次读取的是转换数据的高位字节,第二次读取的是低位字节。假如通道信息要作为数据输出的一部分,那么,应将ADS8364的ADD引脚也接到VCC。读取数据时,需要对ADS8364的每个通道进行三次读操作。第一次读取通道和数据信息,后两次分别读取高位和低位数据。

3.3 ADC的初始化操作

触发ADS8364的复位引脚RST可以确保读指针指向第一个数据位置。作为TMS320F2812初始化的一部分,由TMS320F2812的通用输入输出口GPIOF0提供给ADS8364的引脚RST。当系统时钟稳定后,被触发为低电平,从而确保了从ADC输出的数据对应于通道A0、A1、B0、B1、C0、C1的排列。

ADS8364的片选CS是一个有源低电平输入信号。当CS为高时,并行输出引脚处于高阻态。当CS为低时,并行数据线反映了输出缓冲器的当前状态。为了正确地从ADS8364的并行数据总线上读取数据,ADS8364必须被片选CS选中后才能进行读操作。

ADS8364的读(RD)信号端也是有源低电平信号。当CS为低时,在读信号(RD)的下降沿,ADS8364 中寄存器的内容将被更新。这意味着在每个读序列之前,RD信号必须被触发,这样才能更新输出缓冲器。通过TMS320F2812的中断子程序将ADS8364的RD引脚置低可以保存输入的数据,之后可再将RD引脚置高。

ADS8364与TMS320F2812的连接图

4 初始化编程

(1)头文件(.H)的编写:主要用来定义片内寄存器以便函数中引用。

例如:系统控制与状态寄存器的定义:

此外头文件中还声明一些全局函数和常量。

例如:extern void InitAdc(void); //初始化ADC函数

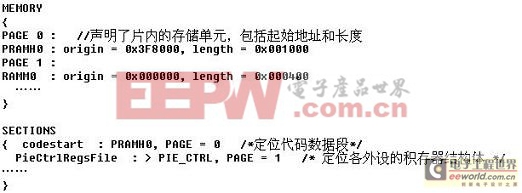

(2)命令文件(.CMD)的编写:该文件中用到了两个伪指令MEMORY和SECTIONS。

MEMORY伪指令用来标示实际存在的目标系统中可被使用的存储器范围。

SECTIONS伪指令用来定位一些代码和数据块。

部分代码:

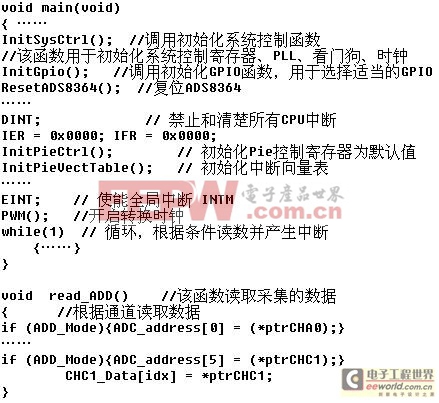

(3)主程序及中断程序:

5 结语

本文以ADS8364模数转换芯片为基础,讨论了ADS8364和TMS320F2812的接口设计和工作原理,介绍了TMS320F2812控制芯片的最小系统设计、ADS8364和TMS320F2812的连接、初始化程序三部分内容。该设计方案在电机控制、多轴定位系统、多通道数据采集等场合有着广泛的应用。

评论