USB接口内部结构

PDIUSBD12内置的串行接口引擎SIE,实现了全部的USB协议层,完全由硬件实现而不需要固件的参与。该模块的功能包括:同步模式的识别、并行/串行转换、位填充/解除填充、CRC校验/产生、PID校验/产生、地址识别和握手评估/产生。

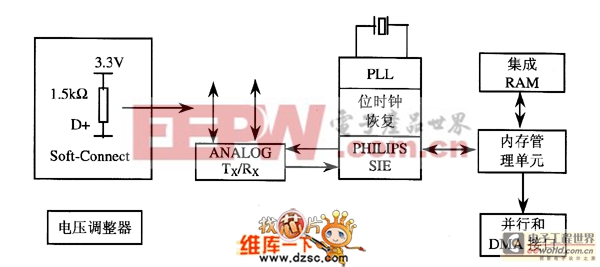

PDIUSBD12的内部结构如图所示。

图 PDIUSBD12的内部结构框图

其中:

·模拟收发器:集成的收发器接口可通过终端电阻直接与USB相连。

·电压调整器:片内集成了一个3.3V的调整器用于模拟收发器的供电。

·PLL:片上集成了6MHZ到48MHZ时钟乘法,允许使用低成本的6MHZ晶振,电磁干扰也由于使用低频晶振而降低。

·位时钟恢复:位时钟恢复电路采用4倍过采样原理,从输入的USB数据流中恢复时钟,能跟踪USB规定范围内的抖动和频漂。

·Soft-CONnect:高速设备与USB的连接是通过1.5kΩ上拉电阻将D+实现的。1.5kQ上拉电阻集成在USB芯片内,默认状态下不与Voc相连。连接的建立通过ARM发送命令来实现,这就允许ARM在决定与USB建立连接之前完成初始化时序。

USB总线连接可以重新初始化而不需要拔出电缆。

·Good-Link:提供良好的USB连接指示。在枚举中,LED指示灯根据通信的状况间歇闪烁。当USB成功地枚举和配置后,LED指示灯将一直点亮。在USB的数据传输过程中,LED将闪烁;在挂起期间,LED熄灭。这种特性为USB器件、集线器和USB通信状态提供了用户友好的指示。作为一个诊断工具,它对隔离故障的设备很有用,降低了现场支持和热线的成本。

·存储空间管理单元(MMU)和集成RAM:在以12Mb/s的速率传输并与ARM相连时,MMU和集成RAM作为USB之间速度差异的缓冲区。这∷就允许ARM以它 自己的速率对USB信息包进行读写。

·并行和DMA接口:对ARM处理器而言,PDIUSBD12看起来就像一个带8位数据总线和一个地址位(占用2个位置)的存储器件。它支持独立的和分时复用的地址和数据总线,还支持主端点与本地共享RAM之间直接读取的DMA传输,以及单周期和突发模式的DMA传输。

评论