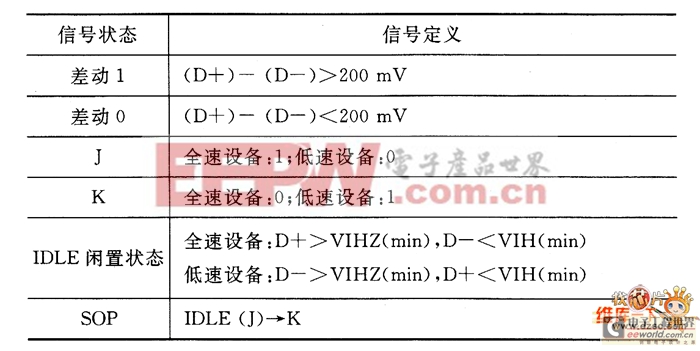

低速与全速的USB总线状态

表 USB D+与D-电位变化的定义

其中,IDLE闲置状态,是说明此时没有驱动器被激活。在全速引线上,D+是正电压的,反之,在低速引线上,D一是正电压的。而当设各插上后,集线器可以通过检查在闲置总线上的电压,立即决定这个设各是低速或全速的。因此,回复状态,则是当设各在中止状态时,以K状态来表示脱离了原先的状态。

此外,单端0(Single-Ended Zero,SE0)与单端1(Single-Ended ONe,SE1)也是另一个USB总线的重要特性。其中,单端0是意味着,D+与D一同时都是逻辑低电位。总线可以通过单端0来切入EOP(End of Packet)、脱离以及重置状态。单端1则是单端0的另一个互补特性。也即是,D+与D一同时都是逻辑低电位,则无效的总线状态,应该是不曾发生的。

根据表的定义,可以知道当设各一连接上去后,D+与D-的其中一条信号线一定会趋近Vdc,另一条则接地,此时设各称为处于J状态,这也就是它的闲置状态。而一旦有激活的信号进来,则切入转换为K状态,在这个时刻也可视为进入了SOP(Start-of-Packet)状态封包开始的状态。每一个传输的低速或全速设各的封包是以SOP所起始的。

相对的,EOP(End of-Packet)则是指当接收器已经在单端0延续了至少一个位的时间,且紧接着随后跟随J状态维持至少一个位时间的总线状态。而这个接收器可以选择性地定义J状态所需的最短的时间。在这个接收器中,单端0状态是近似2个位的宽度。当然,照字面上的意思,每一个所传输的低速或高速的封包都是以EOP来做结束的。

此外,USB的脱离状态(disconnect state)意指当下端接口维持单端0状态延迟至少2.5 μS的时间,就可称之为脱离状态。相对的,所谓的连接状态(connect state)则是当下端接口的总线已经切.人闲置状态至少2.5 μS,但不超过2.0 ms时,称之为连接状态。

至于重置(reset)状态,则是单端0维持超过10 ms时,这个设各必须在重置状态中。而设各在单端0状态已经延续了近2.5 ms后,可以切人重置状态。当一个设各离开重置状态时,它就必须以正确的速度来加以操作,并且必须以预设的地址0来响应各种通信工作。

所以对于用户来说,一些USB的若干总线状态的定义是需要加以理清的。例如,差动0/1、单端0/1、J/K状态、SOP/EOP、中止/回复、脱离/连接与重置状态等。这些都关系到USB整个总线的动作。

评论