汽车电子的EMC设计方案

汽车电子处于一个充满噪声的环境,因此汽车电子必须具有优秀的电磁兼容(EMC)性能。而汽车电子的EMC设计中最主要的是微处理器的设计,作者将结合实际设计经验,分析噪声的产生机理并提出消除噪声的方法。

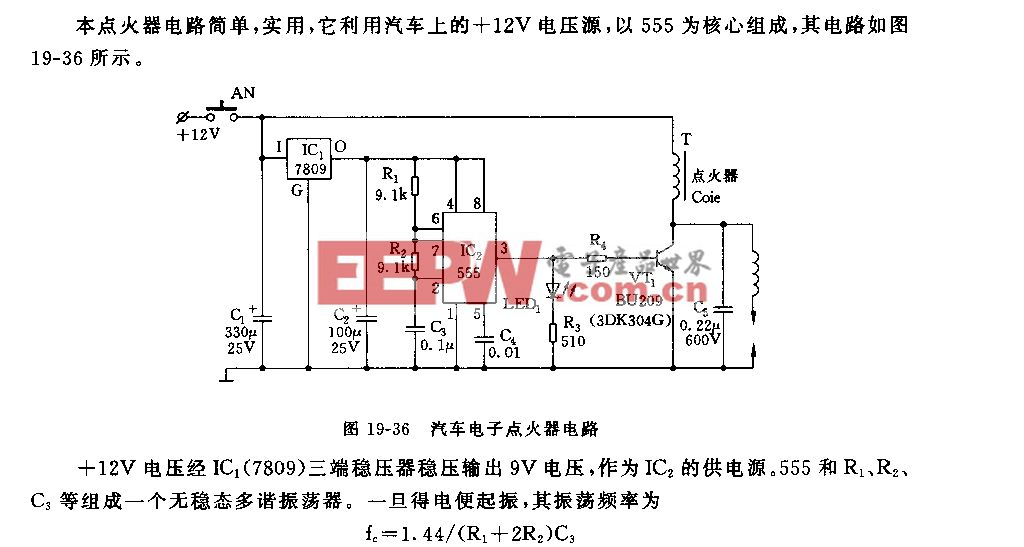

汽车电子常常工作环境很恶劣:环境温度范围为-40oC到125oC;振动和冲击经常发生;有很多噪声源,如刮水器电动机、燃油泵、火花点火线圈、空调起动器、交流发电机线缆连接的间歇切断,以及某些无线电子设备,如手机和寻呼机等。

汽车设计中一般都有一个高度集成的微控制器,该控制器用来完成大量的计算并实现有关车辆运行的控制,包括引擎管理和制动控制等。汽车电子设计不仅需要在这种噪声环境中实现对MCU的保护,同时也必须规范MCU模块设计,确保MCU模块发射的噪声满足相关的规范。

在概念上,电磁兼容性(EMC)包含系统本身对噪声的敏感性以及噪声发射两个部分。噪声可以通过电磁场的方式传播从而产生辐射干扰,也可以通过芯片上或者芯片外的寄生效应传导。

在大多数汽车控制系统设计中,EMC变得越来越重要。如果设计的系统不干扰其它系统,也不受其它系统发射影响,并且不会干扰系统自身,那么所设计的系统就是电磁兼容的。

在美国出售的任何电子设备和系统都必须符合联邦通讯委员会(FCC)制定的EMC标准,而美国主要的汽车制造商也都有自己的一套测试规范来制约其供应商。其它的汽车公司通常也都有各自的要求,如:

SAE J1113(汽车器件电磁敏感性测试程序)给出了汽车器件推荐的测试级别以及测试程序。

SAE J 1338则提供关于整个汽车电磁敏感性如何测试的相关信息。

SAE J1752/3和IEC 61967的第二和第四部分是专用于IC发射测试的两个标准。

欧洲也有自己的标准,欧盟EMC指导规范89/336/EEC于1996年开始生效,从此欧洲汽车工业引入了一个新的EMC指导标准(95/54/EEC)。

检查汽车对于电磁辐射的敏感性,应该确保整个汽车在20到1000MHz的90%带宽范围内参考电平限制在24V/米的均方根值以内,在整个带宽范围以内的均方根值在20V/米以内。在测试过程中要试验驾驶员对方向盘、制动以及引擎速度的直接控制,而且不允许产生可能导致路面上任何其他人混淆的异常,或者驾驶员对汽车直接控制的异常。

由于芯片几何尺寸不断减小,以及时钟速度的不断增加都会导致器件发射超过500MHz的时钟谐波,因此EMC设计非常重要。如摩托罗拉公司最新基于e500架构的微控制器MPC5500系列,该芯片采用0.1微米工艺技术,时钟频率为200MHz。

此外,产品成本的要求迫使生产商设计电路板时不使用地层并尽可能减少器件数量,汽车设计工程师将面对非常严格的设计约束挑战。设计的电子系统必须高度可靠,即使一百万辆汽车中有一辆存在一个简单的故障都是不允许的。没有考虑EMC设计而召回所有汽车的事实证明这种做法不仅损失巨大,而且影响汽车厂商的声誉。

在电磁兼容设计中,“受害方”的概念通常指那些由于设计缺乏EMC考虑而受到影响的部件。受害部件可能在基于MCU的PCB或者模块的内部,也可能是外部系统。通常的受害部件是汽车免持钥匙入车 (Keyless-Entry)模块中的宽带接收器或者是车库门开启装置接收器,由于接收到MCU发出的足够强的噪声,这些模块中的接收器会误认为接收到了一个遥控信号。

汽车收音机通常也是受害部件:MCU可能产生大量的FM波段谐波,严重降低声音质量。分布在汽车中的其它模块也可能受到类似的影响,基于MCU的模块产生的发射噪声经由线缆传播出去,如果MCU产生足够强的噪声对文本和语音进行干扰,那么无绳电话和寻呼机也容易受到干扰。

EMC设计

很多EMC设计技术都可以应用到电路板和SoC设计中。最具共性的部分就是传输线效应,以及布线和电源分布网络上的寄生电阻、电容和电感效应。当然,SoC设计中存在许多与芯片自身相关的技术,涉及基底材料、器件几何尺寸和封装等。

首先了解传输线效应。如果发送器和接收器之间存在阻抗不匹配,信号将产生反射并且导致电压振铃现象,因而降低噪声容限,增加信号串扰并通过容性耦合对外产生信号发射干扰。IC上的传输线尺寸通常非常小,因此不会发射噪声或者受到辐射噪声的影响,而电路板上的传输线尺寸通常比较大,容易产生这种问题,最常用的解决办法是使用串联终结器。

在SoC设计中,噪声主要通过寄生电阻和电容来传导,而不是以电磁场的方式辐射。CMOS芯片通过一种外延工艺实现极低电阻基底的方法来增强抗闭锁的能力,而基底的底侧为基底噪声提供了一种有效的传导路径,使得很难将噪声源同敏感节点在电气上分隔开来。

许多并行的p+基底触点(contact)为阻性耦合噪声提供了一个低阻抗路径。在n阱和p沟道晶体管p基底的侧壁以及底部之间会形成寄生电容,因而产生容性耦合噪声,并且在n沟道晶体管的基底和源区之间形成pn结(见图1)。

单个pn结电容非常小,在一个VLSI的SoC设计中并行的电容总和通常是几个纳法,在连接到电源网络之前将源区和基底直接连接可以短路掉这个电容。这种技术还消除了进入基底的瞬时负电流而导致的体效应(body effect)。体效应会增加耗尽区,并导致晶体管的Vt变高。同样的技术也可以应用于n阱p沟道晶体管,以减小容性耦合噪声。

然而,包含层叠晶体管的数字电路或者模拟电路通常都需要隔离源区。在这种情况下,增加Vss到基底或者Vdd到基底的电容能够降低噪声瞬态值。对模拟电路设计来说,体效应通过改变偏置电流和信号带宽降低了电路性能,因此需要使用其它解决办法,如阱隔离。对数字电路,采用单一的阱最理想,可以降低芯片面积。通过认真的设计可以对体效应进行补偿。

基底噪声的另一个来源是碰撞离化(impact-ionization)电流,该噪声跟工艺技术有关,当NMOS晶体管达到夹断(pinch-off )电压时就会出现这种情况。碰撞离化会在基底产生空穴电流(正的瞬间电流)。

通常,基底噪声的频率范围可能高达1GHz,因此必须考虑趋肤效应。趋肤效应是指导体上随着深度的增加感应系数增大,在导体的中心位置达到最大值。趋肤效应会导致片上信号的衰减以及信号在芯片p+基底层的失真。为最大程度减小趋肤效应,要求基底厚度小于150微米,该尺寸远远小于某些基底允许的最小机械厚度,然而更薄的基底更易碎。

噪声源

微控制器内部存在四种主要的噪声源:内部总线和节点同步开关产生的电源和地线上的电流;输出管脚信号的变换;振荡器工作产生的噪声;开关电容负载产生的片上信号假象。

许多设计方法可以降低同步开关噪声(SSN)。穿透电流是SSN的一个主要来源, 所有的时钟驱动器、总线驱动器以及输出管脚驱动器都可能受到这种效应的影响。这种效应发生在互补类型的反相器中 ,输出状态发生变化时p沟道晶体管和n沟道晶体管瞬间同时导通。确保在互补晶体管导通之前关断另一个晶体管就可以实现穿透电流最小,在大电流驱动器的设计中,这可能要求一个前置驱动器来控制该节点信号的转换率。

切断不需要使用模块的时钟也可以降低SSN。很明显,该技术同具体应用十分相关,应用该技术可以提高EMC性能。在类似摩托罗拉的MPC555和565这样高度集成的微控制器芯片中,所有芯片的外围模块都具有这样的功能。

评论