USB2.0接口IP核的开发与设计

缓存控制器( Buffer Controller)

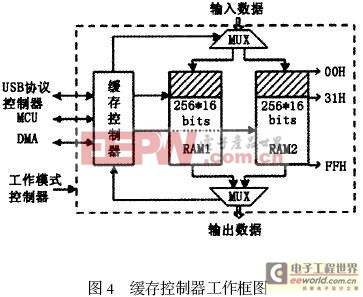

缓存控制器负责暂时存储接收或发送的数据,这些数据来自设备端的外部SDRAM或者主机。考虑到USB 2. 0 高速数据的传输要求,减小存储或读取数据的等待时间,本文采用了双缓冲区的缓存结构,硬件电路可以自动在两个缓冲区间进行转换,这样就可以同时对不同RAM分别读写,减少等待时间,提高了传输效率。不同的传输方式应该有不同的专用缓冲区(主要是区别控制传输和其他传输方式) ,但是为了节省RAM的硬件开销,本文采用了控制传输和其他传输方式缓冲区复用的结构。这种缓存结构也是整个USB 2. 0 接口硬件设计电路的特点之一。如图4 所示,在控制传输时,使用每个RAM地址为00H—31H 的存储空间,因为控制传输的最大数据包容量为32 ×16 位;在其他传输方式时,使用每个RAM地址为00H—FFH的存储空间,数据包的最大容量为256 ×16 位。由此可知,每个RAM的大小为4 种传输方式中最大数据包的容量———512 字节。

本文设计的缓存结构要求缓存控制器对不同的传输方式加以区分,相应增加了一些控制逻辑的复杂度。对于控制传输,数据是在USB 协议控制器和MCU 之间传输;对于其他传输方式,数据则是在USB 协议控制器和DMA(Direct Memory AccESS) 之间传输。总体来说,这种缓存结构是非常合理且有效的:节省硬件开销,而且保证传输速度。

MCU(Micro Control Unit)

MCU 采用的是51 系列的89C52 ,这部分是固件程序,负责协助完成控制传输,即USB 设备功能与设置配置的工作,利用MCU 可以降低硬件复杂度和硬件开销。在控制传输中,利用MCU 的中断程序来及时处理相应的数据交换,在批量传输时,MCU 几乎不参与工作,这是因为其工作速度较慢,不能满足大量数据传输对速度传输要求,影响传输效率。因为这部分不是硬件电路设计,所以就不再赘述了。

测试方案及测试结果

测试电路

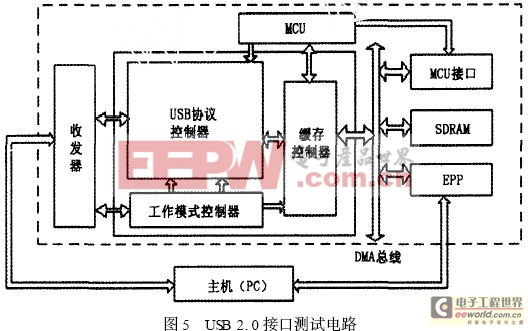

设计了一个测试电路来验证USB 2. 0 接口电路功能的正确性,如图5 所示。在原USB 2. 0 接口电路的基础上,添加了MCU 接口、DMA(Direct Memory Access) 、EPP(Enhanced Parallel Port) 和SDRAM。MCU 负责控制整个电路系统中各个模块的协调工作。这个测试电路实际上基于数码相机电路系统,USB 为该系统与主机的接口电路。

在测试USB 上传数据给主机时,主机先通过EPP 将数据下载到SDRAM中,然后缓存控制器通过DMA总线将数据从SDRAM中读出来,传送给USB 协议控制器,经过USB 协议控制器的打包处理,数据通过收发器传送给主机。通过上传到主机的数据和原数据的对比,就可以验证传送数据的正确性。

下传数据则和上传数据的验证过程类似. 或者直接通过USB 先下传然后再上传来验证数据的正确性。值得一提的是,MCU 接口、DMA ,EPP 和SDRAM这几个模块没有使用收发器芯片提供的30 MHz 时钟,而是使用了另外的系统时钟(13. 5 MHz/ 27 MHz/ 54 MHz) ,这样可以保证在USB 接口电路没有连接到主机或处在挂起状态(收发器此时也处在挂起状态,不提供时钟) 时,主机可以自由地将数据通过EPP 上传或下传到SDRAM中,而不必受USB 接口电路工作与否的限制,便于整个系统的测试工作。这样使得缓存控制器和DMA 之间的数据传输变为异步的工作模式,增加了一些处理的复杂度。图6 为USB 2. 0 接口电路FPGA 验证的验证平台。

测试结果

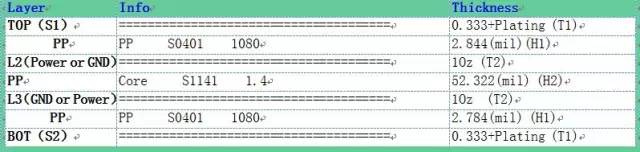

上述硬件电路使用ISE 软件综合后下载到Xilinx 的SPARTAN2XC2S2002PQ208AFP0049 ,其规模大小为20 万门,该FPGA 芯片的工作电压为3. 3 V。综合结果为:硬件逻辑开销为1670 Slices ,RAM开销为1 KB ,时钟最快可达45 MHz ,这完全能够满足整个USB 2. 0 接口电路30 MHz 的工作频率要求。利用逻辑分析仪和Bus Hound 软件进行相应的逻辑功能分析,通过仔细的测试工作可知,在和主机建立连接后,整个USB 2. 0 接口电路可以和主机正常通信。因为整个电路主要应用于数码相机的专用集成电路中,所以着重测试了控制传输和批量传输这两种数据传输方式。

相应的测试结果为:USB 2. 0 接口电路功能正确,在高速,全速和挂起状态下的功耗(包括收发器以及其他的辅助模块EPP , SDRAM 等) 分别为:584 ,254 ,102 mw。批量传输的有效数据传输速率可以达到100 Mbps ,没有达到当然也不可能达到USB 2. 0 协议所规定的480 Mbps ,这是传输带宽的限制和数据包中冗余信息(包开始符、包结束符、同步字段以及校验码) 的存在所导致的,同时在USB 接口电路内部缓存通过DMA总线和SDRAM交互数据的时候,由于DMA 总线速度的限制,缓存也增加了一定的等待时间。总体来讲,100Mbps 的批量传输速率还是令人满意的。

本文提出的USB 2. 0 接口电路系统,兼顾了软硬件的优缺点,硬件电路与单片机有效结合使用,硬件实现简单,造价低廉. 同时为了实现较高的传输速率,满足USB 2. 0 高速传输的要求,并有效节省RAM,电路采用了不同传输方式缓冲区复用的双缓冲区的缓存结构。在FPGA 的验证过程中,为了实现测试的方便性,部分电路采用了异步的工作模式。整个模块已经通过FPGA 验证,功能正确。现在FPGA 的验证工作已经完成,下一步的任务就是在此基础上实现USB 2. 0 接口电路的芯片设计。

pid控制相关文章:pid控制原理

pid控制器相关文章:pid控制器原理

评论