一种实现载波监听多点接入/冲突检测的多主RS485总线

智能仪表和现场总线的出现标志着工业控制领域网络时代的到来,成为工业控制的主流。目前国际上已经出现了多种现场总线和相应的通信协议,但是其系统造价对于许多中小型应用仍显过高。而RS485总线以其构造简单、造价低廉、可选芯片多、便于维护等特点在众多工业控制系统中得到应用。

1 RS485总线及现有工作方式的特点

RS485总线以双绞线为物理介质,工作在半双工的通信状态下[1],即同一时刻,总线上只能有一个节点成为主节点而处于发送状态,其他所有节点必须处于接收状态。如果同一时刻有两个以上的节点处于发送状态,将导致所有发送方的数据发送失败,即所谓总线冲突。为了避免总线冲突,RS485总线具有以下特点:

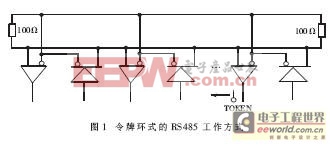

以工作模式来说,一般的RS485总线工作在主从模式下。整个通信总线系统由一个主节点、若干个从节点组成,由主节点不断地轮流查询从节点是否有通信需求。如果 有则将总线控制权交给某一从节点,从节点发送完毕后立刻交还总线控制权。另外还有一种“轮主轮从”的工作方式,即让总线控制权在各个节点间以类似令牌环的方式传递[3],得到控制权的节点成为主节点,其它节点成为从节点。一个节点在发送完数据的同时,将总线控制权交给相邻的节点,而这个节点在处理完本节点的通信需求后再把控制权向下传递。令牌环式的RS485工作方式如图1所示。

有则将总线控制权交给某一从节点,从节点发送完毕后立刻交还总线控制权。另外还有一种“轮主轮从”的工作方式,即让总线控制权在各个节点间以类似令牌环的方式传递[3],得到控制权的节点成为主节点,其它节点成为从节点。一个节点在发送完数据的同时,将总线控制权交给相邻的节点,而这个节点在处理完本节点的通信需求后再把控制权向下传递。令牌环式的RS485工作方式如图1所示。

从通信节点来讲,RS485总线上的节点必须具备将自己的驱动器切换到高阻态的功能?眼1?演,以便在发送完数据后不会对总线状态造成影响。这种驱动器实行发送态—高阻态切换的一个影响是?押从发送数据完毕到设备切换为高阻态,需要一个转换延迟。这个转换延迟是2线制通信中一个很重要的参数。这个时间不能太短,否则发出的字符的最后一部分因为尚未在总线上建立起来而导致丢失。同时这个时间也不能太长,否则在发送端还未转为高阻态时其他设备已经开始发送数据,会导致总线冲突。因此2线制RS485总线上的主设备必须知道所有从设备的反应时间,并保证在从设备反应之前把驱动器设为高阻态,以接收从设备的数据。常用设备的转换延迟是当前波特率发送一个字节的时间。

以上为适应RS485总线的特殊之处而采用的工作方式也引入了一些不足。首先,上面提到的两种总线工作方式在很多对实时性、可靠性要求高的工业控制场合有较大的局限性。主要原因是主从式总线的从节点无发起通信的权利,相互之间的通信需要通过主节点中转。而“轮主轮从”总线上的各个节点由于等待总线控制权的时间未知,实时性也无法保证。同时,如果主从式的主节点或者是“轮主轮从”式的获取令牌的节点出现故障,整个总线的工作将瘫痪,风险过于集中。其次,对驱动器实行“发送态—高阻态”切换以及考虑切换延迟等要求使编程变得复杂。在上电瞬间、CPU损坏或者是程序跑飞的情况下,还需要考虑复杂的故障保护等问题[2],否则将容易引起总线故障。

2 RS485总线上CSMA/CD的实现

为了解决各个节点主动获取总线控制权的问题,人们想到了利用监听总线状态的方式实现总线控制权的本地判断和获取,也就是CSMA/CD协议实际上做的工作[3]。 即所有节点在发送前监听总线上是否有其他节点在发送数据,如果有,就暂时不发送。另外在发送数据的同时,边发送边监听,如果监听到冲突则冲突双方都停止发送。这样做,既能保证每一个节点都具有发起通信的权利,又能尽量减少发生总线冲突的机会,提高整个系统的吞吐量。

即所有节点在发送前监听总线上是否有其他节点在发送数据,如果有,就暂时不发送。另外在发送数据的同时,边发送边监听,如果监听到冲突则冲突双方都停止发送。这样做,既能保证每一个节点都具有发起通信的权利,又能尽量减少发生总线冲突的机会,提高整个系统的吞吐量。

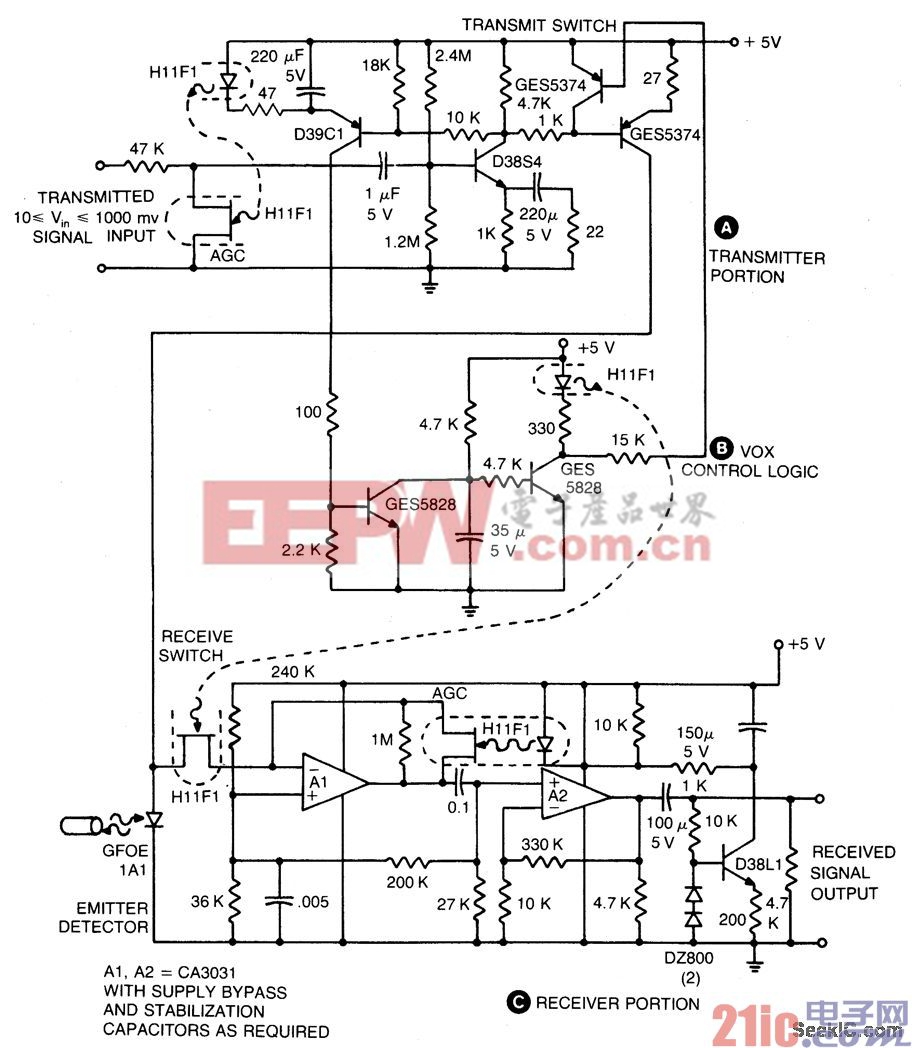

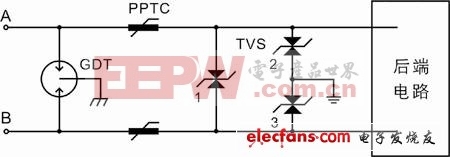

已有的一种实现方法[4]是将总线接收器的输出端反相后接到CPU的外部中断管脚,如图2所示。用触发中断的方式判断总线上是否有数据传输,同时结合定时器中断判断总线是否空闲。如果总线空闲,就获得总线控制权,发送数据;然后用监听自己发送数据的办法判断是否发生总线冲突。该方法解决了总线控制权分配的时延问题,但是需要使用至少4个管脚(INT0、RXD、TXD、驱动器使能管脚),并且占用外部中断和内部定时器中断,需要利用软件监听发送的数据避免总线冲突。系统资源耗费较多,编程复杂,在一些场合的应用也有局限性。本文在以上方法的基础上提出了一种利用硬件监听总线状态的方法,真正实现CSMA/CD协议。同时减少了系统资源的占用率,简化了总线冲突的判断。另外实现了驱动器的无延迟自动切换,进一步提高了系统的实时性。该系统工作稳定、可靠,并且大大提高了通信的实时性,特别适合实时分布式控制的场合。

2.1 系统框图

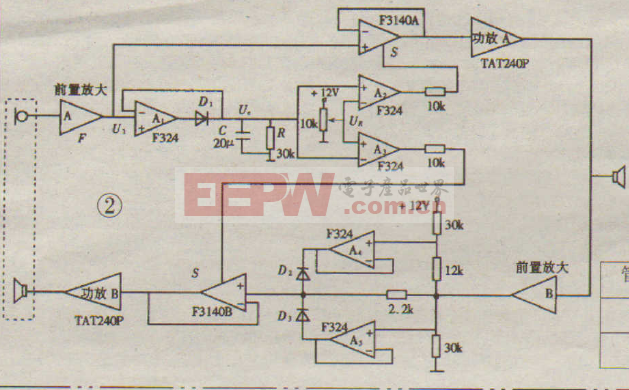

系统由总线状态判断逻辑、驱动器自动切换逻辑两部分组成,如图3所示。系统资源只占用CPU的3个管脚:RXD、TXD、总线状态指示脚,不占用任何中断。在软件实现方面由于采用了硬件判断总线状态而变得非常简单,只需要对标准的232通信程序做微小修改即可。

2.2 总线状态判断逻辑

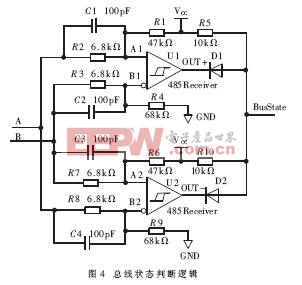

该电路由双RS485总线接收器构成,两个接收器的输出相与后得到总线状态信号。偏置电阻网络的对称形式使得在总线没有被驱动的情况下,两条总线的电平相等。总线状态判断逻辑如图4所示。由于接收器的两个接入点电平不同,所以当总线处于高阻状态或者总线被短路时,两个接收器都是高电平输出,总线状态为高电平。因为A、B线通过6.8kΩ电阻分别接入两个接收器的不同接收端,所以当总线出现任何一个确定的逻辑状态时,都将引起其中一个接收器的输出变为低电平,这样总线状态就变为低电平,表明总线被占用。经过理论计算和EWB仿真,该网络从A、B点看接入阻抗为12.2kΩ,恰好满足RS485协议的接收器输入阻抗要求。

评论