通过FLIX指令结构提高可配置处理器计算性能

指令集的性能更多地是与有用的操作个数相关,而不是与每个执行部件的执行时间或者每个时钟的执行相关。然而,高性能并不能保证系统具有良好的灵活性。指令集的灵活性与不同应用领域的多样性相关,在这些应用中,数据运算能够在指令流中进行有效编码。一个较长的指令字一般可以允许更多数量和更多样性的操作以及操作数标志符在每个指令字中进行编码。

在RISC体系结构中,一条指令通常只对一个原始操作进行编码。在长指令字体系结构中,一条指令可以允许对多个独立的子指令进行编码,每条子指令都有自己的操作和操作数标志符。每条子指令可以是一般的类似于RISC指令的操作或者是一条比较复杂的专用操作。指令字设计的越长,那么对于任意给定的操作数个数和操作个数而言,指令编码就越简单,正交性就越好。

长指令字处理器速度并不总是比RISC处理器快。有时,RISC处理器执行单元的简单性所带来的优点将使得处理器能够以最大时钟频率运行,并且每个时钟周期可以执行几条独特的RISC指令,这将能够弥补因RISC指令集相对简单所带来的损失。尽管如此,在绝大多数要求数据密集型的任务中使用RISC指令集,但是指令集采用超标量方式实现,每个时钟周期执行多条指令,这同长指令字体系结构中那种充分利用程序代码中潜在的指令操作的并行性是一样的。

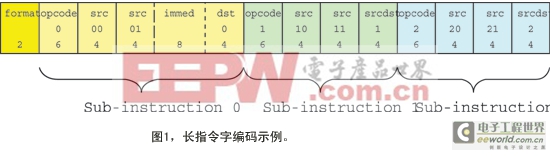

图1表示一个基本的长指令操作编码示例,图中列出一个64位的指令字,该指令字包括三个独立的子指令槽,每个指令槽说明一个操作和若干操作数。第一个子指令(子指令0)有一个操作码和四个操作数说明符(包括两个源寄存器、一个立即数域和一个目的寄存器)。第二个和第三个子指令(子指令1和2)各有一个操作码和三个操作数说明符(两个源寄存器和一个源/目的寄存器)。左边的两位格式域表示各个子指令的特定分组情况。如果处理器支持变长指令编码的话,那么两位的格式域也可以表示整个指令的长度。

显然,系统硬件开销和长指令字是相关的。指令存储器位数越宽,译码逻辑就越大,并且系统就需要更多数量的执行部件,而且寄存器文件(或者寄存器文件端口)实现就必须满足指令并行性的要求。更大的硬件逻辑模块越多,系统优化就越困难,所以,同相对简单和位数较少的RISC指令那样编码相比较,整个系统的最大时钟频率就会降低。尽管如此,追求系统性能和灵活性的优点还是最基本的,尤其是对于那些具有高的程序潜在并行性的数据密集型应用。

在有些长指令字体系结构中,每个子指令都几乎具有完整的独自资源,包括专用执行部件、专用寄存器堆和专用的数据存储器。在另外一些处理器体系结构中,所有子指令共享公用寄存器堆和数据存储器,为保证有效的数据共享系统需要大量的数据端口与公用存储器结构.

长指令字体系结构对于如下问题而言也会有很大不同:一条长指令字该多“长”?对于高端计算机系统处理器(例如英特尔的安腾处理器系列)和高端嵌入式处理器(例如TI公司的TMS320C6400 DSP系列)而言,指令字确实是非常“长”,通常几百位。对于更多的对成本和功耗敏感的嵌入式应用,指令字可能是64位。但是,一旦多个独立的子指令打包成每个指令字后,关键的处理器体系结构原理都是一样的。

代码大小和长指令字

同每条指令只对一个独立操作进行编码的体系结构相比,长指令字体系结构的一个共同问题是代码量大。这是超常指令字VLIW体系结构的一个通病,然而这对于那些片上系统(SoC)设计而言尤其重要,因为SoC系统中的指令存储器通常会占用绝大多数的芯片面积。同那些编译代码有效的体系结构相比,VLIW代码通常需要多占用代码存储容量的两倍到五倍。

VLIW体系结构中程序代码的膨胀问题部分源于指令长度的不灵活性。例如,如果编译器只能找到一个独立操作,其源操作数和执行部件都已经准备好,那么此时编译器就不得不在编码时插入空操作NOP来填满剩下的几个子指令操作域。指令存储已经占用了大部分的嵌入式片上系统SoC硅片面积,因此代码扩充就造成了更大的硬件开销和更低的指令高速缓存性能,或者二者兼而有之。

VLIW代码膨胀问题的第二个根源在于体系结构对常用操作的松散编码,这在VLIW微处理器中是常见的。

然而,长指令并非必然会导致VLIW代码膨胀问题。Tensilica的Vectra LX DSP体系结构中的一个长指令字在指令流中只需要20位就可以说明8个按照单指令流多数据流SIMD方式执行的16位乘加操作MAC,这不包括其它的加载、存储、分支和地址计算指令。

评论