电机数字控制平台方案设计

0 引言

直接转矩控制[1]是目前广为研究的电机控制理论之一,已在异步机上取得了成功,而在同步机方面的应用也已有了一定发展[2]。由于该理论直接对转矩进行控制,故瞬态性能得到了显著的改善。但是,由于其采用的是Bang-Bang控制,控制周期过长会使电流过大;同时大周期会使转矩脉动加大。为了解决这个问题可以从控制策略上加以改进,比如采用SVM-DTC[3]来取代传统DTC方案;也可以在控制平台上加以考虑,提高处理器速度,缩短控制周期。以单个DSP为核心的控制平台(常见的芯片如TI公司的2000系列),由于既要完成复杂的算法,还要执行数据采集、控制信号输出、系统保护以及人机交互等一系列操作,无法有效地缩短控制周期。在综合考虑了各种数字信号处理器的性能之后,决定采用双DSP并行工作的体系结构;并同时考虑到该控制系统的特点,即在每个控制周期内两个DSP之间交换的信息很少,不同于诸如图像采集系统[4]那样,需要大流量的数据交换。由此采取了一系列特殊的设计思想。首先,在芯片的选型上兼顾了各自不同的特点,即专用于电机控制领域的芯片TMS320LF2407A专注于控制;高速通用数据处理芯片TMS320VC33则着眼于复杂算法的实现,从而充分利用了各自的特点。其次,针对电机控制这一特定领域,需要采集的数据相对较少,同时反馈的也只是计算结果,即PWM波发送策略,并无大量中间结果,因此,需要考虑的重点是控制方法的实现,和数据采集的实现必须占用尽可能少的资源。同时由于数据量较少,可以用较小的代价来实现数据的冗余,使得数据处理时更加灵活和方便,DSP之间并不一定保持同步工作状态。为了实现两个DSP之间的数据交换和通信,选择了双口RAM作为两者之间的媒介。并从硬件和软件上相互配合,避免存储空间争用[5]的同时,使得数据存储过程尽量少耗费各种资源。

1 硬件系统构成

TMS320LF2407A最突出的特点在于其事件管理器模块:共有两个事件管理器EVA及EVB,提供了8个16位脉宽调制(PWM)通道。这些都是针对电机控制而设计的,在PWM波的产生上相当方便可靠;可编程的PWM死区控制可以防止上下桥臂同时输出触发脉冲而导致直通。同时每个模块还提供了两个外部引脚PDPINTA和PDPINTB,当该引脚上出现低电平时事件管理器模块将快速关闭相应的PWM通道,起到保护作用。片内模数转换模块为数据采集提供了高性能的A/D转换器,最小转换时间只有500ns。由于转换时间是整个控制周期的组成部分之一,快速A/D对于缩短控制周期是非常有利的。

TMS320C3X系列DSP芯片是一种性能价格比很好的浮点处理芯片,具有很高的数据处理速度。片内部分拥有34K×32位的RAM,在程序运行期间,所有的数据都位于其中,从而能够充分发挥哈佛总线结构所带来的数据吞吐量大、运算快的优点。在算法实现上,由于采用了浮点计算格式,将使计算精度得到提高;采用编程语言C会使程序编写效率大大改善,这对于需要用复杂算法实现的控制策略来说是很重要的。

双口RAM的特点在于具有两组相互独立的地址线、数据线和控制线,片内包含的控制逻辑解决了三个重要的问题:处理器之间的信号关系(中断逻辑);两个CPU正在使用同一地址时的时间关系(仲裁逻辑)和把一块存储器临时分配到某一边的硬件支持(旗语逻辑),从而保证双机之间数据、信号交流的正确进行。

仲裁逻辑(忙逻辑) 每块CY7C025允许两个CPU同时读取任何存储单元(包括同时读同一地址单元),但是不允许同时写或者一读一写同一地址单元,否则就会发生错误。双口RAM中已经有相应的仲裁逻辑电路来解决这一问题:先行稳定的地址端口通过仲裁逻辑电路优先读写,同时内部电路使另一个端口的BUSY信号有效,并在内部禁止对方访问,直到本端口的操作结束。BUSY信号可以作为CPURDY信号的来源,从而使得CPU处于等待状态。

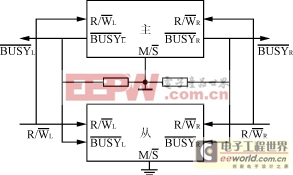

当双口RAM单片使用的时候,问题相对简单,但是,在现代数字系统中,由于数据总线的宽度往往可以达到32位甚至更宽,这就需要多片双口RAM来进行位扩展。此时如果出现同时访问,将有多块双口RAM处于工作状态,如果依然象单片工作时那样,每块双口RAM都使用自己的仲裁逻辑,则很可能出现一种情况,即第一片仲裁使得BUSYL变低,而第二片仲裁使BUSYR变低,这样两边的CPU都会处于等待状态。为了避免这种情况的发生(BUSY信号死锁),可以使用主从模式,使得当多块芯片一起工作时,只使用主片的仲裁逻辑,并迫使从片跟随主片。主从模式的电路连接如图1所示。

图1 主从连接电路

主芯片的BUSY信号接上拉电阻作为输出,从芯片的BUSY信号作为写禁止输入,当主芯片处于BUSY状态时,从芯片接收这个状态,同样处于忙状态,从而避免了死锁的发生。

中断逻辑 另一个重要的内部电路结构,它允许双CPU通过端口直接进行通信。CY7C025最高位的存储单元1FFF作为右边端口的中断信箱,

次高位存储单元1FFE作为左边端口的中断信箱。各CPU可以读取双方的中断信箱,但只能写对方的中断信箱。当一端写入对方的中断信箱时,对方就会产生一个中断信号;读自己的中断信箱则清除自己的中断信号,读对方的中断信箱不会清除中断信号。

旗语通信逻辑 可以使双口RAM暂时指定一块存储区,只供一端的CPU使用,称之为独占模式。CY7C025配置了独立于RAM阵列的8个旗语锁存器,用于标志双口RAM是否处于独占模式。独占模式也可以用来避免地址仲裁问题,因为,它是一种使两边不同时使用同一地址的方法,通常也叫做软件仲裁。

控制平台结构框图如图2所示。

图2 双DSP系统结构框图

电机由IPM来驱动,霍尔元件检测相关物理量,通过信号调理电路给A/D转换器,转换结果由LF2407A存储于双口RAM中,并由VC33读取用于计算。调理的同时保护电路也进行相应的检测,在意外状况发生时随时切断触发信号。VC33将获取的数据进行分析和计算,所有的数据处理都由VC33完成,只将计算结果反馈给LF2407A,并由此产生相应的控制信号,通过接口电路来控制IPM工作。同时预留了D/A及串口输出等相关外围电路,用于实现显示、检测、与其它系统通信等各项功能。LF2407A和VC33优势互补,并行工作,控制周期的长短主要取决于算法实现时间。原有的控制软件(以C32为控制平台)需要100μs左右,在采用了新的控制平台后,整个控制周期减小到20μs左右。

2 双端口RAM存储争用解决方案

在双机的数据交流过程中,存在存储空间争用问题,常见的解决方案有如下几种。

——硬件方案 最简单的方法就是上面提到的使用双口RAM内部的仲裁逻辑,要求两边的CPU都具有RDY引脚,从而插入相应的等待周期。对于8098单片机,DSP都具有这样的资源,而且只需要硬件支持,相对简单。如果不具备RDY引脚,如8031单片机,则不能采用此种方法。

——中断方案 需要硬件和软件的同时支持。将双口RAM的左右中断信号输出引脚和CPU的外部中断输入引脚相连,并编写相应的中断子程序。

评论